CPLD пояснив: Посібник з програмованих логічних пристроїв

У динамічному світі електронного дизайну складні програмовані логічні пристрої (CPLDS) виділяються як універсальні інструменти, безперешкодно змішування адаптивності, точності та ефективності.Ці пристрої революційні конструкції схеми, вводячи програмовані макро -комірки та домінуючу матрицю взаємозв'язку, що дозволяє створити складні логічні функції з надзвичайною надійністю.З їх заснування у 1980 -х роках до їх ключової ролі в сучасних галузях, таких як мережа, автомобільна та аерокосмічна, CPLDS виявили необхідність для вас, щоб шукати як гнучкості, так і ефективності.Ця стаття копається в подорож CPLDS, їх відмінних особливостей, практичних застосувань та методологій програмування, які роблять їх наріжним каменем у цифровій логічній конструкції.Каталог

Огляд CPLD

У межах домініону складних програмованих логічних пристроїв (CPLD) один виявляє складний гобелен програмованих логічних макро -клітин, переплетених через домінуючу матрицю взаємозв'язку.Ці макро -комірки (MC) та вхід/вихід (вводу/вивод) одиничні лінії дозволяють спритно проектувати схеми, налаштовуючи структури для унікальних функцій.На відміну від пристроїв, які здивовані їх складними термінами взаємозв'язку, CPLD використовують нерухомі металеві проводи.Ця характеристика дарує їм послідовну та передбачувану поведінку годинника, що робить прогнозування термінів більш надійними та точними.

Подорож та використання

1970 -ті роки оголосили появу програмованих логічних пристроїв (PLD), що сприяє руху до програмованих макро -одиниць.Цей зсув ввів достатню гнучкість дизайну, виділяючи їх від статичних цифрових схем, хоча їх корисність спочатку була обмежена на простіші схеми.Поява CPLD в середині 1980-х років революціонізувало цей пейзаж, прокладаючи шлях для складних конструкцій ланцюгів.З тих пір вони вплітали в тканину галузей, таких як мережа, автомобільна електроніка, обробка з ЧПУ та аерокосмічні системи.Ви можете нагадати про те, як CPLDS спрощували процеси, які колись вимагали ретельної ручної праці, відзначаючи чудовий стрибок у ефективності.

Відмінні якості CPLD

CPLDS розрізняють себе завдяки своєму пристосованому програмуванню, великій інтеграції, можливостям швидкого розвитку та широкомасштабним застосуваністю, а також економічними виробничими витратами.Вони звертаються до тих, хто має мінімальний апаратний досвід, слугуючи надійними та безпечними продуктами, які не потребують вичерпних тестувань.Як свідчить про їхню доблесть у масштабних конструкціях схеми, CPLDS відіграє ключову роль у розробці прототипу та обслуговує запуск нижче 10 000 одиниць, втілюючи корисну компетентність для вас.Сміття, з якою CPLD налаштовуються на вимоги проекту, що розвиваються, часто заробляє їм вдячність, підкреслюючи їх фактичну універсальність у динамічних умовах.

Методи застосування

Ці інтегровані схеми дозволяють розробити логічні функції, пристосовані до їх потреб, використовуючи як схеми, так і мови опису обладнання на платформах розробки.Наприклад, у розробці автовідповідача, схематики та описів обладнання готуються та складаються на комп’ютері.Використовуючи кабель завантаження, код переноситься на CPLD для програмування в системі, що включає тестування, усунення несправностей та вдосконалення конструкцій.Потім успішно створені конструкції масово виробляються шляхом реплікації мікросхем CPLD.У таких проектах, як системи світлофора, повторення процесу проектування стає необхідним, подібно до відновлення будинку для відновлення його новизні.Ця повторювана методологія часто закладає основу для оволодіння, підвищення як навичок, так і впевненості.

Провідні варіанти

Протягом багатьох років такі компанії, як Altera, ґрата та Xilinx, представили видатні лінії CPLDS.Примітні приклади включають Altera EPM7128s, Ґрат LC4128V, і Xilinx XC95108 .Ці моделі знайшли видатні ролі в різних глобальних додатках.Ті, хто мав честь працювати з цими окремими продуктами, часто зауважує про тонкі, але потужні відмінності, які оптимізують конкретні функціональні можливості.Це відображає тонкий процес відбору, який впливає на конкретні вимоги проекту, де кожен варіант має свою унікальну привабливість.

Ідентифікація та класифікація FPGA та CPLD

|

Аспект |

CPLD |

FPGA |

|

Логічна формування поведінки |

Формуйте логічну поведінку з використанням структури терміну продукту.

Приклади: Серія решітки ISPLSI, серія XILINX XC9500, Altera Max7000s

Серія, серія ґрунтових махів |

Формуйте логічну поведінку за допомогою методу пошуку таблиці.

Приклади: Спартанська серія Xilinx, Altera Flex10K, Acex1k Series |

|

Придатність |

Підходить для алгоритмів та комбінаційної логіки

Краще з обмеженими тригерами та багатими умовами продукту |

Підходить для послідовної логіки, краще працює

структури, багаті тригерами |

|

Затримка часу |

Конструкція безперервної електропроводки забезпечує рівномірну та

передбачувані затримки часу |

Сегментована структура електропроводки призводить до непередбачуваних термінів

затримки |

|

Гнучкість програмування |

Виправлені внутрішні схеми модифіковані для програмування.

Використовується логічне програмування на рівні блоків |

Внутрішня проводка модифікована для програмування.Логіка

Програмування на рівні воріт дозволяє збільшити гнучкість |

|

Інтеграція |

Нижча інтеграція порівняно з FPGA |

Більш висока інтеграція з більш складною структурою електропроводки та

Логічна реалізація |

|

Простота використання |

Простіше користуватися програмуванням через E2PROM або FastFlash.

Жодна зовнішня мікросхема пам'яті не потрібна |

Вимагає зовнішньої пам'яті для зберігання програмування

інформація, що призводить до більш складного використання |

|

Швидкість та передбачуваність |

Швидша швидкість та краща передбачуваність термінів через

Круглий взаємозв'язок між логічними блоками |

Повільніша швидкість і менш передбачувані терміни через

Програмування на рівні воріт та розподілене взаємозв'язок |

|

Технологія програмування |

Використовує програмування E2PROM або Flash Memory.Дані програмування

зберігається, коли система вимикається.Підтримує програмування на

Програміст або в системі |

На основі програмування SRAM.Дані про програмування втрачаються, коли

Система вимикається і повинна бути перезавантажена.Підтримує динамічний

конфігурація |

|

Конфіденційність |

Пропонує кращу конфіденційність |

Забезпечує меншу конфіденційність |

|

Споживання електроенергії |

Як правило, більш високе споживання електроенергії, особливо з

більш висока інтеграція |

Нижнє споживання електроенергії порівняно з CPLD |

Мови програмування CPLD

Аналізи, як складні програмовані логічні пристрої (CPLDS) запрограмовані, є наріжним каменем у розробці універсальних апаратних рішень.Історичні методи програмування CPLDS покладаються на діаграми сходів або мови опису апаратних засобів (ЛПВЩ), при цьому переважаючи на Verilog HDL та VHDL.Вибрана мова може формувати як стратегію дизайну, так і оперативну ефективність впровадження.

• Verilog HDL: Verilog HDL плекається за його простим синтаксисом та надійними можливостями моделювання, що відображає методології, що використовуються в цифровій логічній конструкції.Його інтеграція з інструментами електронної проектної автоматизації (EDA) дозволяє безперешкодно проводити синтез та моделювання.Спостерігається, що Синтаксис Cerilog, схожий на Verilog, знижує бар'єр для входу для тих, хто має програмування, прискорюючи подорож від дизайну до розгортання в широкому спектрі промислових секторів.

• VHDL: VHDL забезпечує більш витончений та виразний варіант для програмування ЛПВЩ.Часто це вибір для проектів, які вимагають ретельної документації та суворої перевірки типу, рис, що оцінюються в аерокосмічній та оборонній галузях.Ви можете зауважити, що, незважаючи на потенційну складність VHDL в менших проектах, його дисциплінована структура підтримує створення надзвичайно надійних конструкцій, необхідності в середовищах, де домінуюча безпека.

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Транзистори NMOS: проектування, експлуатація та додатки

на 2024/12/29

Швидке перетворення Фур'є (FFT): Революція цифрової обробки сигналів

на 2024/12/29

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147764

-

USB-C Pinout та функції

на 2000/04/18 111987

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

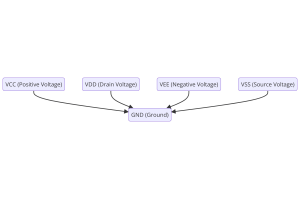

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83751

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79542

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66949

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63090

-

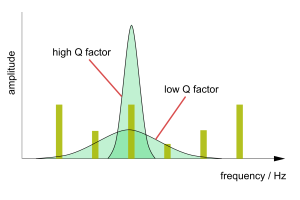

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63028

-

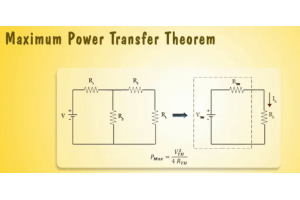

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54092

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52172