Сегмент коду (CS) Реєстр у сегментації пам'яті процесора: Повне керівництво

Процесор виконує програми, отримуючи доступ до інструкцій, що зберігаються в пам'яті, а ключовою частиною цього процесу є регістр сегмента коду (CS).Реєстр CS необхідний у процесорах, які використовують сегментовану модель пам'яті, особливо в старих системах, таких як архітектура X86.Ця стаття пояснює, як регістр CS працює з вказівником інструкцій (IP) для управління пам'яттю та чому розуміння сегментації пам’яті все ще важливо.Каталог

Який реєстр сегмента коду (CS)?

Сегмент коду (CS) - це спеціалізований реєстр у процесорі, який містить стартову адресу (або базову адресу) сегмента коду в пам'яті.Сегмент коду - це спеціальна область пам'яті, яка містить виконуваний код програми.Таким чином, реєстр CS вказує на місце в пам'яті, де зберігаються інструкції щодо програми, що дозволяє процесору отримувати та виконувати ці інструкції.Роль реєстру CS стає зрозумілішою, коли ми розглядаємо його взаємозв'язок з іншим важливим реєстру: вказівником інструкцій (IP).Поки реєстр CS містить стартову адресу сегмента коду, IP -регістр відстежує адресу зміщення наступної інструкції, яка буде виконана в цьому сегменті.Разом регістри CS та IP утворюють логічну адресу, яка дозволяє процесору визначити точне розташування наступної інструкції в пам'яті.Наприклад:

Cs = базова адреса коду сегменту

Ip = адреса зміщення наступної інструкції

У поєднанні процесор обчислює фізичну адресу як CS: IP Щоб знайти та виконати наступну інструкцію.

Сегментована модель пам'яті

Щоб зрозуміти, чому існує реєстр CS, він повинен зрозуміти сегментовану модель пам'яті, яка зазвичай використовувалася в старих архітектурах, таких як процесори X86.У цій моделі пам'ять поділяється на сегменти, кожен з яких служить різній меті:

• Сегмент коду (CS): зберігає виконуваний код.

• Сегмент даних (DS): зберігає змінні та дані, що використовуються програмою.

• Сегмент стека (SS): керує функціональними дзвінками, локальними змінними та контрольним потоком.

• Додаткові сегменти): використовується для додаткового зберігання даних.

Сегментована модель пам'яті була розроблена для забезпечення структурованого підходу до управління пам'яттю, що полегшує розділення пам'яті на різні регіони для коду, даних та стека.Цей підхід дозволив процесорам більш ефективно керувати пам'яттю та забезпечив кращий захист пам'яті, зберігаючи різні типи даних в окремих сегментах.У ранніх обчислювальних системах процесор міг отримати лише обмежену кількість пам'яті одночасно.Сегментована модель пам'яті дозволила програмістам працювати з більшою кількістю пам'яті, розділивши її на менші, більш керовані розділи.Ця конструкція також допомогла зменшити розмір адрес, оскільки реєстри сегментів можуть утримувати базові адреси, тоді як компенсації (як IP) будуть меншими значеннями, доданими до бази.Хоча сучасні процесори часто використовують модель плоскої пам'яті, де вся пам'ять трактується як єдиний безперервний простір, принципи сегментації все ще впливають на дизайн процесора сьогодні.Насправді деякі сучасні системи продовжують використовувати сегментацію для таких цілей, як захист пам'яті та віртуалізація.

Взаємозв'язок між регістрами CS та IP

У центральному блоці обробки комп'ютера (процесор) взаємозв'язок між реєстру CS (код сегмента) та реєстрами IP (вказівника інструкції) є важливим для процесу отримання та виконання інструкцій.Разом ці два регістри визначають розташування наступної інструкції в пам'яті та переконайтесь, що процесор точно знає, що виконати на кожному кроці потоку програми.

Реєстр CS містить стартову адресу певного сегмента в пам'яті, де знаходиться виконуваний код.Ця адресація на основі сегмента необхідна в сегментованих архітектурах пам'яті, що дозволяє процесору розділити пам'ять на логічні розділи для різних типів даних, таких як код, стек та сегменти даних.З іншого боку, IP -регістр діє як вказівник, який відстежує наступну інструкцію для виконання в поточному сегменті коду.Реєстр IP містить значення зміщення, яке вказує, наскільки далеко від початкової точки сегмента коду знаходиться наступна інструкція.

На практиці цей взаємозв'язок працює наступним чином: CPU спочатку зчитує адресу, що зберігається в реєстрі CS, щоб визначити вихідну точку сегмента коду в пам'яті.Потім він використовує значення, що зберігається в регістрі IP, для обчислення точного розташування наступної інструкції, додавши зміщення IP до базової адреси, наданої реєстру CS.Поєднання цих двох значень, базової адреси з реєстру CS та зміщення з реєстру IP, дає адресу фізичної пам'яті, де зберігається наступна інструкція.

Після обчислення фізичної адреси процесор отримує інструкцію з пам'яті, розшифровує її та виконує.Після виконання регістр IP оновлюється, щоб вказати на наступну інструкцію послідовно, а процес повторюється.Цей безперервний цикл отримання, декодування та виконання інструкцій є основним механізмом, за допомогою якого процесор здійснює програми.Регістри CS та IP працюють разом, щоб переконатися, що процесор точно знає, де шукати в пам'яті, щоб знайти наступну інструкцію для виконання.Цей взаємозв'язок корисно для підтримки правильного потоку виконання програм, особливо в системах з сегментованою архітектурою пам'яті.

Чому реєстр CS має значення в програмуванні?

Реєстр CS чудово підходить для програмування низького рівня та розробки систем, особливо в середовищах, які покладаються на сегментовані моделі пам'яті.Він визначає межі сегмента коду, де зберігаються виконувані інструкції, і допомагає забезпечити, щоб програми працювали в призначеному просторі пам'яті.Правильне управління цими межами сегмента необхідні, щоб уникнути помилок та підтримувати стабільність системи.Одне поширене питання з поганим управлінням сегментом - це порушення доступу.Вони трапляються, коли програма намагається завести пам'ять поза визначеним сегментом коду, що призводить до збоїв або несподіваної поведінки.Наприклад, якщо програма перевищує розмір сегмента коду, вона може перезаписати сусідню пам'ять, що призводить до пошкоджених даних або нестабільних продуктивності.

Інший ризик - непередбачувана поведінка програми через неправильне використання реєстру CS.Коли процесор виконує інструкції з ненавмисних областей пам'яті, система може поводитися непередбачувано або повністю зламатися.Це була часта проблема в старих системах, яка використовувала сегментовану пам'ять, наприклад, ранні архітектури X86, де програмістам доводилося ретельно керувати регістрами, такими як CS, DS (сегмент даних) та SS (сегмент стека).Хоча сучасні системи часто використовують моделі плоскої пам'яті, розуміння регістра CS залишається важливим для роботи в вбудованих системах, проектуванні операційної системи або інших галузях, які потребують прямого контролю пам'яті.У цих сферах ефективне управління межами пам'яті забезпечує надійність системи, запобігає пошкодженню даних та дозволяє уникнути важко діагностованих помилок.Для програмістів низького рівня освоєння реєстру CS є ключовою частиною стабільного, ефективного програмного забезпечення.

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Bitstreams та Bittorrent: вивчення децентралізованого обміну файлами, технологіями та юридичними наслідками

на 2025/01/6

Порушення послуг переривання (ISR) у вбудованих системах: поняття, важливість та дизайн

на 2025/01/6

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147764

-

USB-C Pinout та функції

на 2000/04/18 111984

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

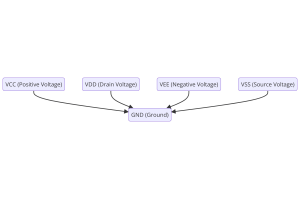

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83743

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79538

-

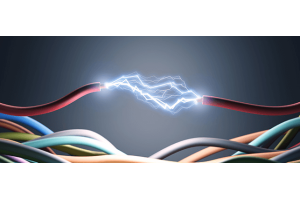

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66948

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63087

-

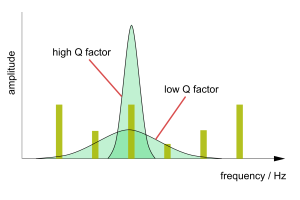

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63028

-

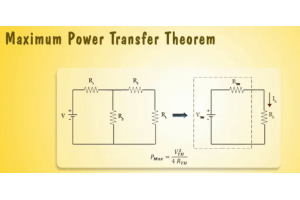

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54092

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52171