Вичерпний посібник з тестових балів: інструменти та методи перевірки цифрової системи

Цей посібник досліджує Testbenches, ключовий інструмент для перевірки програмного забезпечення, який імітує умови для тестування входів та перевірки виходів.Testbenches відіграють певну роль у визначенні помилок на початку розробки, підвищення надійності програмного забезпечення.За допомогою практичних прикладів та розумінь ця стаття висвітлює їх використання, методи та важливість у створенні міцних, ефективних цифрових систем.Каталог

Роль тестів у валідації цифрової системи

TestBench - це компонент у процесі перевірки цифрової системи.Це не просто інструмент для генерування входів та перевірки результатів, він служить всебічною рамкою, яка імітує умови для оцінки надійності, функціональності та поведінки цифрових систем до їх розгортання у цій галузі.Створюючи контрольовані середовища для систем тесту стресу з широким спектром вхідних сценаріїв, Testbenchs допомагає вам визначити потенційні недоліки дизайну на початку життєвого циклу розробки, задовго до того, як система буде введена у виробництво.Це раннє виявлення помилок та вразливості необхідне для зменшення дорогих помилок, забезпечення дотримання специфікацій ефективності та підвищення загальної надійності системи.

Окрім перевірки правильності відповідей системи, тестові палички відіграють певну роль у оцінці регламенту, проблем часу та механізмів обробки помилок, гарантуючи, що система може правильно діяти навіть у екстремальних або несподіваних умовах.Завдяки автоматизованому тестуванню та моделюванню, Testbenchs сприяють більшій якості програмного забезпечення, покращеної продуктивності та коротших циклів розвитку, дозволяючи ітеративним тестуванням без ручного втручання.Вони служать захистом від невдач, які можуть статися після розгортання, забезпечуючи надійність та надійність цифрових систем.

Ключові компоненти тестового стека та їх функції

Щоб краще зрозуміти, як діють тест -сфери, важливо вивчити компоненти, які роблять їх ефективними.Добре складений Testbench працює, керуючи двома основними завданнями: генерування входів (подразників) та перевірки результатів.Давайте детально розглянемо кожен компонент.

Генерування стимулів

Генерація стимулів передбачає створення набору вхідних сигналів, що імітують умови для перевірки поведінки цифрової системи.Ці входи повинні бути як точними, так і реалістичними для того, щоб система піддавалася різноманітним сценаріям, з якими вона може зіткнутися на практиці.Розглянемо базовий модуль оперативної пам’яті як приклад.TestBench повинен подавати конкретні входи до модуля та спостерігати за його виходами, щоб переконатися, що він поводиться так, як очікувалося.Ключові входи для модуля оперативної пам’яті зазвичай включають:

• CLK (годинник): приводить в рух системи системи.

• ADDR (адреса): Вказує, яке місцезнаходження даних для доступу.

• WEN (запишіть увімкнення): контролює, чи записуються дані в пам'ять.

• Дані: фактична інформація, що записується в модуль.

Вихід, відомий як DataOut, являє собою результат внутрішніх операцій модуля.Ретельно написавши, як ці входи доставляються та моніторинг даних, ви можете перевірити, чи система виконує правильно за різними сценаріями.Подумайте про створення стимулів як про встановлення тестового сценарію в лабораторії.Подібно до того, як вчені ретельно контролюють умови для спостереження за хімічними реакціями, цифрові дизайнери виготовляють точні входи, щоб спостерігати, як реагує система.

Перевірка виходу

Перевірка виходу - це процес перевірки того, що фактичні результати системи відповідають очікуваним результатам.Цей крок має вирішальне значення для ловлення помилок рано, перш ніж вони перетворюються на більші проблеми.Інші використовують перевірку виходу, щоб підтвердити, що система відповідає її передбачуваній функціональності та виконує послідовно в різних умовах.Перевірка виходу включає як автоматизовані, так і ручні перевірки.Наприклад:

• Автоматизовані інструменти перевірки: такі інструменти, як ModelsIm та Quartus, дозволяють автоматизувати тестування, де системні виходи порівнюються з очікуваними результатами.Це прискорює процес перевірки та зменшує помилку.

• Ручна перевірка (необов’язково): Для більш складних сценаріїв може знадобитися ручні перевірки, щоб забезпечити висвітлення конкретних регламентів.

Інструменти та методи реалізації TestBench

Кварт: моделювання візуального вводу/виводу

Кварт забезпечує графічний інтерфейс, який візуально влаштовує входи та спостерігає виходи.Цей метод може бути корисним для початківців або для систем, які потребують більш практичного візуального підходу.Дозволяючи взаємодіяти з моделюванням за допомогою графічного середовища, квартал допомагає демістифікувати взаємозв'язок між входами та результатами, що полегшує розуміння того, як поводиться цифрова система в часі.Однією з ключових сильних сторін кварталу є те, що він ідеально підходить для початківців.Його інтуїтивний, візуальний інтерфейс забезпечує прямий спосіб побачити, як входи впливають на результати без необхідності великих знань із сценарієм чи програмуванням.Зворотній зв'язок, який він пропонує, допомагає легше зрозуміти поведінку ланцюгів, що робить його корисним інструментом для нових для дизайну цифрової системи.Однак квартал має свої обмеження.Налаштування моделювання в кварталі може зайняти багато часу, особливо для більш складних конструкцій.Інструмент менш гнучкий порівняно з інструментами моделювання на основі сценаріїв, які можуть запропонувати більше варіантів налаштування та автоматизації.Для роботи над масштабними або дуже детальними системами ця відсутність гнучкості може поставити виклик.

Modelsim: Текстове моделювання за допомогою сценаріїв

Modelsim застосовує інший підхід до моделювання, визначивши пріоритет текстового введення за допомогою сценаріїв.Створіть тестові сценарії за допомогою сценаріїв Verilog (.V) або VHDL (.VHD), а не візуально розташовуючи входи та виходи.Цей метод забезпечує більш точність та контроль.Замість того, щоб покладатися на графічний інтерфейс, ви визначаєте, як систему слід протестувати за допомогою детальних сценаріїв, що дозволяє збільшити налаштування та автоматизацію в процесі моделювання.Однією з ключових сил ModeliM є гнучкість, яку він пропонує.Використовуючи сценарії, ви маєте більше контролю над тестовими сценаріями, що дозволяє їм створювати складні та точні моделювання.Після того, як дизайнер знайомий із синтаксисом та робочим процесом, налаштування моделювання може бути набагато швидшим порівняно з використанням графічних інструментів, таких як Quartus.Можливість повторного використання та модифікації сценаріїв також додає його ефективності, особливо у великих проектах.Однак текстовий підхід Modelsim має певні обмеження.Це вимагає твердого розуміння синтаксису Verilog або VHDL, що може створити виклик для початківців, які не знайомі з мови опису обладнання.Як результат, Modelsim має більш круту криву навчання порівняно з більш візуальними інструментами моделювання.Новому користувачам може бути важко розпочати роботу, але з практикою точність та гнучкість, пропоновані сценарієм, можуть стати цінним надбанням.

Теорія мости та практики у перевірці

Testbenches служать мостом між теоретичними конструкціями та додатками, імітуючи, як поводитиметься цифрова система в різних умовах, включаючи корпуси краю та несподівані входи.У цифровому дизайні часто важко передбачити, як система буде працювати на практиці, заснована виключно на теоретичних моделях.Testbenchs закривають цю прогалину, дозволяючи виходити за межі абстрактних концепцій дизайну та оцінити поведінку системи в контрольованому, імітованому середовищі.Однією з ключових переваг використання інструментів моделювання в Testbench - це миттєвий зворотний зв'язок, який вони надають під час налагодження.Такі інструменти, як Multisim або Modelsim, пропонують візуальні уявлення про поведінку системи, показуючи, як зміни входів впливають на виходи з часом.Цей зворотний зв'язок дозволяє швидше визначати проблеми, відстежувати помилки до їх першопричини та відповідно відрегулювати їх конструкції.Наприклад, якщо система не відповідає обмеженням часу або виявляє несподівану поведінку при певних вхідних послідовностях, TestBench може виділити ці недоліки негайно, задовго до того, як система буде фізично побудована.Визначаючи проблеми на початку циклу проектування, тестові палички зменшують потребу в дорогій переробці та фізичному прототипуванні, впорядкування процесу перевірки.Ця перевірка на ранній стадії допомагає забезпечити, щоб цифрові системи були як функціонально правильними, так і стійкими до умов, що робить їх більш надійними та зменшуючи ризик відмови після розгортання.Таким чином, Testbenches виступає практичним інструментом для перетворення теоретичних конструкцій у надійну.

Вдосконалена архітектура Testbench

Розширені тестові палички виходять за рамки простого тестування введення-виводу, включивши додаткові компоненти для управління складними системами.Стандартний тестовий ступінь включає три ключові частини: a Генератор стимулів Для створення вхідних сигналів, Дизайн, що перевіряється (DUT), що є фактичним апаратним забезпеченням, а також Вихідний монітор Це перевіряє результати проти очікуваних результатів.Ці компоненти працюють разом, щоб забезпечити більш ретельну та точну перевірку цифрових конструкцій.

Удосконалення точності тесту передбачає використання методів, які забезпечують надійно в різних сценаріях. Рандомізоване тестування Вводить непередбачувані схеми введення для перевірки стабільності системи в різних умовах. Тестування краю випадків Орієнтується на прикордонні ситуації, коли система, швидше за все, зіткнеться з помилками.Нарешті, Регресійне тестування Залучає повторні тести після змін, щоб підтвердити, що жодних нових питань не було введено, гарантуючи, що система з часом залишається послідовною та без помилок.

Сценарії тестів

Для створення ефективних та надійних тестів у Verilog або VHDL дотримуйтесь ключових найкращих практик.Почніть просте, потім розширюйте, перевіряючи базову функціональність спочатку і поступово додаючи більш складні сценарії.Використовуйте коментарі та документацію, щоб зробити ваші сценарії простішими для розуміння та підтримки, чітко пояснюючи кожен розділ.Нарешті, автоматизуйте, де це можливо, щоб заощадити час та зменшити помилки, використовуючи петлі та функції для обробки повторюваних завдань та шаблонів введення.

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Цифрова фазова петля (DPLL): дизайн, компоненти та операції

на 2025/01/7

Еволюція та вплив архітектури RISC в сучасних обчисленнях

на 2025/01/7

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147778

-

USB-C Pinout та функції

на 2000/04/18 112027

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

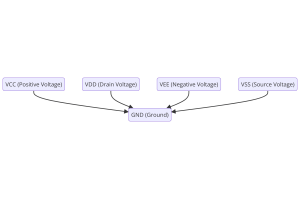

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83780

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79578

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66969

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63107

-

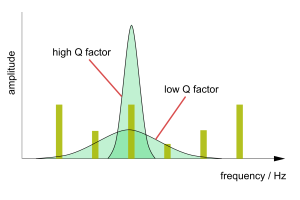

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63041

-

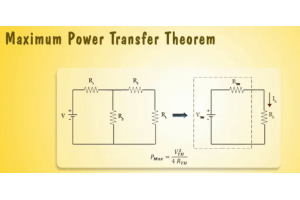

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54097

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52191