EP1C4F400C8 FPGA: Особливості, специфікації, програмування та альтернативи

Якщо ви працюєте з програмованою логікою, EP1C4F400C8 дає вам практичний баланс ефективності та витрат.У цій статті ви дізнаєтесь, що таке FPGA, її ключові функції, такі як логічна ємність, пам'ять та параметри вводу/виводу, а також як його структура підтримує надійний дизайн.Ви також побачите його специфікації, програми в системах, процес програмування та те, як він порівнюється з подібними частинами.Каталог

Що таке EP1C4F400C8?

З EP1C4F400C8 є членом сім'ї циклону FPGA (раніше Altera) Intel (раніше Altera), розробленої як економічно вигідне та надійне програмоване логічне рішення.Побудований на процесі SRAM 0,13 мкм, цей пристрій пропонує помірну логічну щільність та гнучкі параметри вводу/виводу в компактному пакеті FBGA-400.Сімейство циклонів, що включають такі пристрої, як EP1C3, EP1C6, EP1C12 та EP1C20, була створена для збалансування продуктивності та доступності для масштабованих конструкцій, що дозволяє легкої міграції між рівнем щільності та пакетами.Відомий стабільністю та широким прийняттям, він залишається надійним вибором у застарілих дизайнах.

Шукаєте EP1C4F400C8?Зверніться до нас, щоб перевірити поточні акції, час виконання та ціни.

Моделі CAD EP1C4F400C8

Символ EP1C4F400C8

EP1C4F400C8 Слід

3D -модель EP1C4F400C8

Функції EP1C4F400C8

• Логічна здатність

EP1C4F400C8 пропонує близько 4000 логічних елементів, організованих у 400 логічних блоків масиву (лабораторії).Це робить його придатним для конструкцій середнього діапазону, які потребують помірної логічної щільності, зберігаючи ефективність витрат.

• Вбудована пам'ять

Він інтегрує приблизно 76,5 кбіт вбудованої пам'яті.Ця внутрішня оперативна пам’ять підтримує функції буферизації, зберігання та невеликої пам'яті, зменшуючи потребу у зовнішніх компонентах пам'яті у багатьох конструкціях.

• Високий введення/вир

Пристрій забезпечує 301, налаштований користувачем шпильки вводу/виводу у своєму пакеті FBGA на 400 м'ячів.Цей високий кількість PIN -коду дозволяє багатим підключенням для складних систем, що потребують декількох периферійних інтерфейсів.

• Широка підтримка стандартів вводу/виводу

Він підтримує кілька стандартів вводу/виводу, включаючи LVTTL, LVCMOS, SSTL-2, SSTL-3 та диференціальні LVDS.Ця гнучкість дозволяє FPGA безпосередньо взаємодіяти з різноманітними сучасними логічними сім'ями та пристроями пам'яті.

• Високошвидкісна диференціальна сигналізація

Завдяки підтримці LVD до 640 Мбіт / с, FPGA вирішує швидкі вимоги передачі даних.Це робить його практичним для таких додатків, як високошвидкісні зв'язки та швидкі цифрові інтерфейси.

• Управління годинником за допомогою PLLS

Чіп інтегрує дві фазові петлі (PLLS) та вісім глобальних годинних мереж.Ці функції дозволяють точне генерацію годин, множення та контроль тремтіння для критичних термінів.

• Операція ядра з низькою напругою

Працюючи при номінальній напрузі 1,5 В, пристрій врівноважує продуктивність із меншим споживанням електроенергії.Цей рівень напруги був оптимізований для технології CMOS 0,13 мкм, що використовується в її виготовленні.

• Гнучкі напруги вводу/виводу

FPGA підтримує напруги вводу/виводу 1,5 В, 1,8 В, 2,5 В та 3,3 В у різних банках.Ця універсальність дозволяє йому взаємодіяти як із застарілими, так і з сучасними системними компонентами.

• Конфігурація на базі SRAM

Як і інші циклоні FPGA, він базується на SRAM і вимагає реконфігурації при кожному живленням.Це забезпечує гнучкість для оновлень, але також вимагає зовнішнього пристрою конфігурації або контролера.

• Підтримка стиснення біцтрового

EP1C4F400C8 підтримує стиснене завантаження біт -кістки під час конфігурації.Це зменшує зовнішні вимоги до пам'яті та прискорює час конфігурації.

• Відповідність PCI

Він включає вбудовану підтримку стандартів PCI (33/66 МГц, 32/64-біт).Ця функція дозволяє пристрою безпосередньо інтегровуватися в системи, що вимагають взаємодії PCI без додаткової логіки мосту.

Структура лабораторії циклону

На діаграмі відображається структура блоку логічного масиву (лабораторія), що використовується в циклоні FPGA, як EP1C4F400C8.Кожна лабораторія підключається до мережі взаємозв'язків: зв'язки рядків, взаємозв'язки стовпців та локальні взаємозв'язки, які маршруту сигнали між логічними елементами та іншими блоками.Прямі зв’язки зв'язку забезпечують швидкі шляхи низької затримки до сусідніх лабораторій, покращуючи продуктивність часу в шляхах сигналу.Ця архітектура важлива, оскільки вона врівноважує гнучкість маршрутизації з ефективністю, що дозволяє FPGA обробляти складні конструкції, зберігаючи швидкість та область оптимізовано.

Діаграма банків вводу/виводу циклону

Діаграма ілюструє банківську структуру вводу/виводу циклонів FPGA, таких як EP1C4F400C8.Пристрій розділений на чотири банки вводу/виводу, кожен з яких працює від власної шини живлення, що дозволяє змішувати різні стандарти напруги в межах однієї FPGA.Усі банки підтримують широкий спектр стандартів вводу/виводу, включаючи LVTTL, LVCMOS, LVDS, RSDS та SSTL, тоді як банки 1 і 3 також підтримують PCI 3,3-V для сумісності зі застарілими системами.Ця гнучка архітектура вводу/виводу є важливою, оскільки вона забезпечує безперебійну інтеграцію з різноманітними зовнішніми пристроями та інтерфейсами, що робить FPGA пристосованою до різних програм.

Технічні характеристики EP1C4F400C8

|

Тип |

Параметр |

|

Виробник |

Altera/Intel |

|

Серія |

Cyclone® |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Кількість лабораторій/CLB |

400 |

|

Кількість логічних елементів/клітин |

4000 |

|

Загальні шматочки оперативної пам’яті |

78,336 |

|

Кількість вводу/виводу |

301 |

|

Напруга - постачання |

1,425 В ~ 1,575 В |

|

Монтажний тип |

Поверхневе кріплення |

|

Робоча температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / кейс |

400-BGA |

|

Пакет пристроїв постачальника |

400-FBGA (21 × 21) |

|

Базовий номер товару |

EP1C4 |

Програми EP1C4F400C8

1. Цифрова обробка сигналів (DSP)

EP1C4F400C8 можна запрограмувати для виконання таких завдань, як фільтрація, FFT та модуляція сигналу.Його поєднання логічних елементів та вбудованої пам'яті робить її придатною для швидкісної обробки.Це дозволяє йому замінити традиційні мікросхеми DSP гнучким рішенням FPGA, яке можна перепрограмувати для різних алгоритмів.

2. Вбудовані та управління системами

У промислових та вбудованих системах цей FPGA часто використовується для впровадження спеціальних контролерів, секвенсорів та державних машин.Його перебудована логіка дозволяє адаптувати поведінку обладнання саме до системних потреб.Інтегруючи логіку управління всередині FPGA, кількість зовнішніх компонентів зменшується, підвищуючи надійність та зниження витрат.

3. Зв'язок та мостовий інтерфейс

Пристрій підтримує кілька стандартів вводу/виводу і може діяти як міст між різними протоколами зв'язку.Він часто використовується для підключення PCI, LVDS, SDRAM та інших інтерфейсів безперешкодно в системі.Це робить його дуже корисним для мережевого обладнання, вбудованих контролерів та конверсій Legacy-Modern Interface.

4. Збір та обробка даних

З високою доступністю вводу/виводу та гнучкою пам'яттю, EP1C4F400C8 добре підходить для систем збору даних.Він може безпосередньо взаємодіяти з АЦП та датчиками, обробляти дані вчасно та підготувати їх до зберігання або передачі.Такі застосування поширені в медичних інструментах, тестовому обладнанні та наукових вимірювальних пристроях.

Подібні частини EP1C4F400C8

|

Специфікація |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Виробник |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

Сім'я FPGA |

Циклон (EP1C4) |

Циклон (EP1C4) |

Циклон (EP1C4) |

Циклон (EP1C4) |

Циклон (EP1C4) |

Циклон (EP1C4) |

|

Логічні елементи (LES) |

4000 |

4000 |

4000 |

4000 |

4000 |

4000 |

|

Вбудована пам'ять (шматочки) |

~ 76,5 кбіт |

~ 76,5 кбіт |

~ 76,5 кбіт |

~ 76,5 кбіт |

~ 76,5 кбіт |

~ 76,5 кбіт |

|

Шпильки вводу/виводу |

301 |

301 |

301 |

301 |

249 |

97 |

|

Пакет / кейс |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-TQFP |

|

Швидкість |

C8 |

C8 |

C8 |

C6 (швидше) |

C8 |

C8 |

|

Основна напруга |

1,5 В |

1,5 В |

1,5 В |

1,5 В |

1,5 В |

1,5 В |

|

Температура експлуатації.Діапазон |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C

|

Етапи програмування EP1C4F400C8

Перш ніж використовувати FPGA EP1C4F400C8, ви повинні завантажити свою конструкцію в пристрій.Програмування передбачає налаштування FPGA з файлом Bitstream, щоб він знала, як поводитися як ваш передбачуваний ланцюг.

1. Виберіть схему конфігурації та встановіть штифти MSLE

Ви починаєте з вибору схеми конфігурації, яка найкраще відповідає вашій установці, наприклад, активних серійних, пасивних серійних або JTAG.Це робиться шляхом встановлення штифтів MSEL на конкретні логічні рівні перед живленням.Кожен режим використовує різні шпильки та протоколи, тому вам потрібно підтвердити сумісність з інструментами дизайну та пам'яттю конфігурації.Правильний вибір тут забезпечує плавний процес конфігурації.

2. Застосовуйте живлення та ініціалізуйте пристрій

Далі ввімкніть ядро FPGA та рейки вводу/виводу в межах зазначених діапазонів напруги.Під час запуску зберігайте штифт Nconfig Low, щоб утримувати пристрій у скиданнях, поки напруги живлення не стануть стабільними.Після стабільності ви випускаєте скидання, а пристрій сигналізує про готовність, керуючи штифтом NSTATUS.Це гарантує, що FPGA належним чином ініціалізується до початку конфігурації.

3. Передайте Bitstream конфігурації

На цьому етапі ви надсилаєте файл даних конфігурації (Bitstream) у FPGA за допомогою вибраної схеми.У активному послідовному або пасивному серійному режимі Bitstream надходить із зовнішнього пристрою пам'яті, тоді як JTAG дозволяє прямувати програмування за допомогою кабелю.Пристрій постійно читається в даних конфігурації, поки він не завершиться.Ваше дизайнерське програмне забезпечення генерує цей Bitstream, щоб відповідати вашим логічним вимогам.

4. Підтвердьте успішну конфігурацію (conf_done)

Коли FPGA закінчує завантаження, він стверджує, що PIN -код Conf_Done показує, що дані конфігурації були успішно отримані.У той же час пристрій виконує внутрішню ініціалізацію, наприклад, очищення регістрів та активація вводу/виводу.Якщо conf_done не вдається зростати, це зазвичай означає, що дані конфігурації або налаштування мають помилку.Спостерігати за цим PIN -кодами - це найпростіший спосіб перевірити, що процес завершений.

5. Виконайте необов’язкову реконфігурацію в системі

Нарешті, у вас є можливість оновити або перепрограмувати FPGA, не видаляючи його з дошки.Використовуючи JTAG або вбудований контролер, ви можете завантажити новий Bitstream безпосередньо, що корисно для оновлення прошивки.Ця гнучкість дозволяє змінювати, налагодити або оновлювати вашу систему навіть після розгортання.Це гарантує, що ваш дизайн на основі FPGA може з часом адаптуватися до зміни вимог.

Переваги та недоліки EP1C4F400C8

Переваги

• Економічний вибір для конструкцій середнього класу

• Висока кількість вводу/виводу порівняно з аналогічними пристроями щільності

• Гнучка напруга та стандартна підтримка вводу/виводу

• Підтримується зрілими інструментами та документацією

• Нижнє використання електроенергії, ніж старі покоління FPGA

Недоліки

• застаріло з обмеженою довгостроковою доступністю

• Нижня логіка та ємність пам'яті проти сучасних FPGAS

• Повільна швидкість роботи та продуктивність вводу/виводу

• Потрібна зовнішня пам'ять для конфігурації при живленні

• Не вистачає вдосконалених функцій, таких як блоки DSP та високошвидкісні приймачі

Розміри упаковки EP1C4F400C8

|

Тип |

Параметр |

|

Тип пакету |

FBGA (масив сітки з толководами) |

|

Кількість |

400 |

|

Куля (E) |

1,0 мм (типовий для циклону EP1C4F400) |

|

Діаметр кулі (B) |

0,45 мм (номінальний) |

|

Розмір пакету (D × E) |

21 мм × 21 мм |

|

Висота упаковки (a) |

2,40 мм (макс) |

|

Товщина підкладки (A2) |

~ 0,40 мм |

|

Товщина кришки цвілі (A3) |

~ 1,90 мм |

|

Висота м'яча (A1) |

0,25 мм (номінальний) |

|

Закріпіть куточок A1 |

Позначений для орієнтації |

|

Макет масиву |

20 × 20 сітки (з кутовими кульками відсутні) |

|

Кріплення |

Поверхневе кріплення (SMD) |

Виробник EP1C4F400C8

EP1C4F400C8 спочатку виготовляли Корпорація Altera, Піонер програмованих логічних пристроїв та технології FPGA.У 2015 році Altera придбала Корпорація Intel, і лінійка продуктів стала частиною групи програмованих рішень Intel (PSG).Сьогодні Intel підтримує ці застарілі пристрої Altera, зосереджуючи розвиток на нових сім'ях FPGA, забезпечуючи безперервність для існуючих користувачів та просуваючи інновації в програмованій логіці.

Висновок

EP1C4F400C8 виділяється як економічно ефективна та універсальна FPGA, яка пропонує міцну продуктивність для конструкцій середнього класу.Завдяки своїм 4000 логічним елементам, вбудованій пам'яті, великій підтримці вводу/виводу та сумісності з декількома стандартами напруги та інтерфейсу, він забезпечує гнучкість у різних програмах.Його архітектура, процес програмування та широка зручність використання в DSP, вбудованих системах та збору даних роблять його практичним вибором, незважаючи на його застарілий статус.Хоча йому не вистачає розширених функцій, знайдених у нових пристроях та стикаються з обмеженою довгостроковою доступністю, він залишається надійним варіантом, який шукає перевірені рішення в масштабованих конструкціях FPGA.

PDF -таблиця

EP1C4F400C8 DATASHEETS:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Які інструменти потрібні для програмування EP1C4F400C8?

Вам потрібне програмне забезпечення Intel Cartus (раніше Altera Quartus II) разом із підтримуваним кабелем програмування, таким як USB-Blaster.Ці інструменти дозволяють створити Bitstream та завантажувати його в FPGA.

2. Чи може EP1C4F400C8 безпосередньо обробляти програми PCI?

Так, він має вбудовану відповідність стандартам PCI (33/66 МГц, 32/64-бітний), що робить його придатним для інтеграції системи на основі PCI, не вимагаючи додаткової логіки мости.

3. Що станеться, якщо під час конфігурації не вдається EP1C4F400C8?

Якщо конфігурація не вдасться, PIN -код Conf_Done не стверджує високо.Зазвичай це вказує на помилку у файлі Bitstream, послідовності напруги або налаштування PIN -коду, і його слід переглянути у вашому проектному потоці.

4. Чи може інтерфейс EP1C4F400C8 безпосередньо з пам'яттю DDR?

Він підтримує кілька стандартів вводу/виводу, але не має рідних інтерфейсів DDR, таких як сучасні FPGA.Можуть знадобитися додаткові дизайнерські міркування або компоненти мостових компонентів.

5. Як EP1C4F400C8 порівнюється з новішими FPGA?

Порівняно з сучасними пристроями, EP1C4F400C8 має меншу швидкість, меншу логічну щільність та меншу кількість вдосконалених функцій.Однак це залишається економічно ефективним вибором для стабільних конструкцій середнього класу, де передові показники не потрібні.

EPM3256AFC256-7 Огляд CPLD: Особливості, Покін, Програмування та програми

на 2025/10/3

ADG432BR ANALOG SWITCH IC: Технічні характеристики, Покін, альтернативи та таблиця даних

на 2025/10/2

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147776

-

USB-C Pinout та функції

на 2000/04/18 112022

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

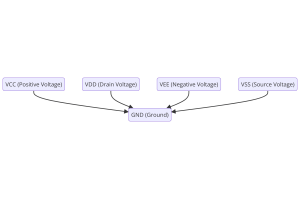

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83777

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79575

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66964

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63104

-

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63041

-

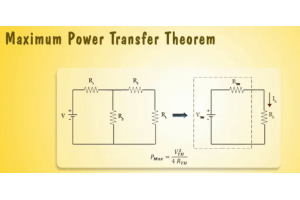

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54097

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52189