EPM7192SQC160-15 CPLD: Особливості, Покін, Програмування та додатки

Цей посібник розповідає про EPM7192SQC160-15, програмовану логічну мікросхему від родини Max 7000S.Це пояснює, що може зробити чіп, як він працює, і де його можна використовувати.Він показує, як мікросхема побудована всередині, що робить кожен штифт, і як він підключається до інших частин.Посібник також включає, де можна використовувати цю мікросхему, як його програмувати поетапно, які інші подібні фішки існують, і хто його робить.Каталог

Що таке EPM7192SQC160-15?

З EPM7192SQC160-15 -це середній діапазон CPLD (складний програмований логічний пристрій) із сімейства Max 7000S, зроблених для надійного цифрового контролю логіки в вбудованих та промислових системах.Цей чіп пропонує 192 макроцелі та близько 3750 логічних воріт, що забезпечує достатню ємність для обробки помірних логічних завдань.Він включає 124 шпильки вводу/виводу, а також працює на 5 В, з підтримкою багатовольтового вводу/виводу для взаємодії з логічними системами 3,3 В та 5В.Його програмована архітектура на основі EEPROM означає, що ви можете перепрограмувати його безпосередньо у своєму ланцюзі за допомогою JTAG, не потребуючи додаткових компонентів або зовнішньої пам'яті.Завдяки ступеня швидкості –15, він підтримує частоту системних годин до приблизно 76,9 МГц, пропонуючи швидку та послідовну продуктивність часу для широких цифрових додатків.Сім'я Max 7000S відома своїми суцільними показниками, пам'яттю EEPROM та гнучкою напругою.

Шукаєте EPM7192SQC160-15?Зверніться до нас, щоб перевірити поточні акції, час виконання та ціни.

EPM7192SQC160-15 CAD Моделі

EPM7192SQC160-15 Символ

EPM7192SQC160-15 Слід

EPM7192SQC160-15 3D-модель

EPM7192SQC160-15 Особливості

192 Макроцеліти: Пристрій включає 192 макроцелі, які служать основними програмованими елементами.Ці макроцелі можуть бути налаштовані для реалізації найрізноманітніших комбінаційних та послідовних логічних функцій, необхідних в цифрових конструкціях.

Приблизно 3750 логічних воріт: Він пропонує еквівалентну логічну ємність близько 3750 воріт, що робить її придатною для логіки управління середньою складністю, державними машинами або логікою клею в вбудованих системах.

Програмність в системі через JTAG: Він має пам'ять на основі EEPROM, яка дозволяє перепрограмувати безпосередньо в системі за допомогою стандартного інтерфейсу JTAG, підтримуючи як стандарти IEEE 1149.1 та IEEE 1532.

Максимальна частота до 125 МГц: Внутрішня логіка може працювати на тактових швидкостях, що досягають 125 МГц, що дозволяє швидко обробляти додатки, чутливі до термінів.

Затримка про поширення 7,5 нс: Чіп пропонує низьку затримку розповсюдження приблизно 7,5 наносекунд, що забезпечує швидку реакцію сигналу від входу на вихід.

Підтримує 5 В постачання з мультивольтом вводу/виводу: Пристрій працює на 5 В ядровому живленню і підтримує мультивольт вводу/виводу, що дозволяє сумувати як з рівнем сигналу 5 В та 3,3 В для легкої інтеграції в системи змішаної напруги.

Програмована швидкість SLOW та вихідні виходи: Ви можете контролювати швидкість краю сигналу для зменшення EMI та вибрати виходи з відкритим збігом для дротової та логіки або перемикання рівня.

Шість глобальних виробничих сигналів: Ці глобальні сигнали управління дозволяють включати або відключати результати в декількох банках вводу/виводу для ефективного управління сигналами.

Налаштовані шльопанці в макроцелі: Кожен Macrocell включає фліп-флоп, який підтримує попередньо встановлений, чіткий, включений годинник та індивідуальний контроль, забезпечуючи посилену гнучкість для послідовної логічної конструкції.

Режим низької потужності: Пристрій включає функцію економії електроенергії, яка може скоротити споживання енергії Macrocell на понад 50%, що корисно для енергоефективних додатків.

Підтримка тестових прикордонних сканів JTAG : Пристрої з 128 або більше макроцеллами, як цей, включають повні функції тестування прикордонних сканів для ефективної діагностики та перевірки рівня дошки.

Біт безпеки для захисту дизайну: Програмований біт безпеки гарантує, що внутрішній дизайн неможливо прочитати або скопіювати, захищаючи інтелектуальну власність.

Сумісна PCI вводу/виводу: Структура вводу/виводу призначена для задоволення електричних вимог PCI, що дозволяє прямувати взаємодію з системами на основі PCI.

Робочий діапазон температури від 0 ° С до 70 ° C: Стандартний діапазон комерційного класу робить цей пристрій придатним для більшості програм у приміщенні та контрольованому середовищі.

EPM7192SQC160-15 PINOUT Діаграма

Ця діаграма показує макет PIN-коду для EPM7192SQC160-15 та подібних пристроїв Altera Max 7000S.Чіп має 160 штифтів, розташованих навколо всіх чотирьох сторін у квадратному пакеті QFP.Шпилька 1 починається в верхньому лівому куті, а цифри йдуть проти годинникової стрілки навколо мікросхеми.Кожна сторона має 40 шпильок.Невелика крапка на верхніх лівих позначках шпильки 1, що допомагає при правильному розміщенні.Назва чіпа в центрі показує, що він сумісний з іншими моделями в одній родині.Цей макет забезпечує багато з'єднань вводу/виводу і корисний для складних логічних конструкцій.

Блок -схема Max 7000S

Ця блок-схема показує внутрішню структуру CPLD Max 7000S, включаючи EPM7192SQC160-15.Чіп поділяється на чотири основні секції під назвою блоки логічного масиву (лабораторія A до D).Кожна лабораторія має 16 макроцелів, які є невеликими логічними одиницями, що використовуються для створення цифрових схем.Разом ці лабораторії обробляють складні логічні операції.

У центрі знаходиться програмований масив взаємозв'язків (PIA), який з'єднує всі лабораторії та дозволяє їм ділитися даними.Кожна лабораторія надсилає та отримує сигнали через 36 каналів, надаючи гнучку маршрутизацію між логічними блоками.По краях є блоки управління вводу/виводу, які пов'язують 6 до 16 штифтів вводу/виводу до кожної лабораторії, що дозволяє пристрою з'єднуватися з іншими частинами системи.

Вгорі відображаються глобальні сигнали управління, такі як годинники та вихідний вихід.Ці сигнали допомагають керувати тим, як дані рухаються всередині мікросхеми та коли результати активні.Загалом, на схемі показано, як EPM7192SQC160-15 організовує свою логіку та з'єднання для підтримки спеціальних цифрових конструкцій.

Технічні характеристики EPM7192SQC160-15

|

Тип |

Параметр |

|

Виробник |

Альтер |

|

Серія |

Max® 7000s |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Програмований тип |

В системному програмованому |

|

Затримка часу TPD (1) Макс |

15 нс |

|

Постачання напруги - внутрішнє |

4,75 В ~ 5,25 В |

|

Кількість логічних елементів/блоків |

12 |

|

Кількість макроцелів |

192 |

|

Кількість воріт |

3750 |

|

Кількість вводу/виводу |

124 |

|

Робоча температура |

0 ° C ~ 70 ° C (TA) |

|

Монтажний тип |

Поверхневе кріплення |

|

Пакет / кейс |

160-BQFP |

|

Пакет пристроїв постачальника |

160-PQFP (28x28) |

|

Базовий номер товару |

EPM7192 |

EPM7192SQC160-15

Вбудована логіка клею системи

EPM7192SQC160-15 ідеально підходить для подолання різних цифрових пристроїв у вбудованих системах.Він може бути використаний для управління зв'язком між мікроконтролами, мікросхемами пам'яті та пристроями вводу/виводу, обробляючи декодування адреси, регулювання шини та регулювання термінів, не потребуючи дискретних логічних ІС.

Державні машини та логіка управління

Завдяки своїм 192 макроцеллам, мікросхема добре підходить для впровадження спеціальних машин стану та логіки управління.Він зазвичай використовується в завданнях автоматизації, контролерів двигуна та системах управління на основі термінів, які потребують надійних та повторюваних переходів стану.

Інтерфейси протоколу зв'язку

Цей CPLD може бути запрограмований для створення або перекладу протоколів зв'язку, таких як UART, SPI, I²C або користувацькі серійні формати.Це дозволяє прості конфігурації та модифікацію без зміни обладнання, що робить його цінним для взаємодії зв'язку.

Попередня обробка цифрового сигналу

Завдяки швидкій логічній швидкості та низькій затримці розповсюдження, він може обробляти прості завдання обробки сигналів, такі як фільтрація, мультиплексування або виявлення краю, перш ніж сигнали досягнуть основного процесора або чіпа DSP.

Переклад інтерфейсу та зміна рівня

Його багатовольтна здатність вводу/виводу підтримує як 3,3 В, так і 5 В.Це робить його придатним для конструкцій, що включають компоненти, що працюють на різних рівнях напруги, що дозволяє безпечним та ефективним перекладом напруги.

Швидкі оновлення прототипування та оновлення

Ви можете використовувати цей мікросхему в системах, які можуть вимагати часті оновлення логіки.Його структура на основі EEPROM та інтерфейс програмування JTAG дозволяє перепрограмувати логіку навіть після того, як плата зібралася.

Тест на рівні дошки та діагностика

Завдяки підтримці прикордонних сканів через JTAG, він перевіряє з'єднання між мікросхемами на друкованій друкованій платі, не потребуючи зондів.Це корисно під час виробництва та діагностики для виявлення пайки або маршрутизації.

EPM7192SQC160-15 Подібні частини

• EPM7192EQC160-20 (Altera)

Цей пристрій є з тієї ж серії Max 7000 і пропонує ті ж логічні ресурси, 192 макроцелі та 124 шпильки вводу/виводу в 160-контактному пакеті PQFP.Він працює з повільнішою швидкістю –20, тобто він має більш тривалі затримки поширення (~ 20 нс), але він все ще відповідає потребам, які не мають часу, конструкції.Це підходяща альтернатива для додатків, де важлива логічна щільність, але надшвидкі терміни не є пріоритетним, що робить його ідеальним для проектів, чутливих до витрат, які все ще потребують функціональної еквівалентності.

• EPM7192SQI160-10N (Altera)

Ця частина також сумісна з логікою з EPM7192SQC160-15, що пропонує однакову кількість макроцеллів та i/OS.Однак він використовує –10 швидкості швидкості, яка підтримує швидшу роботу з вдосконаленими термінами (10 нс затримки розповсюдження).Він також підтримує розширений діапазон температури від –40 ° C до +85 ° C, що робить його чудовою заміною промислових або зовнішніх застосувань.Це робить його ідеальним, коли потрібна більш висока швидкість та екологічна стійкість.

• EPM7192SQC160-7 (Intel)

Як прямий варіант швидкого прискорення EPM7192SQC160-15, версія –7 забезпечує найшвидший показник у сім'ї, із затримкою поширення до 7,5 нс.Він підтримує ту саму конфігурацію PIN-коду, специфікації живлення та логічну щільність, пропонуючи заміну для тих, хто шукає кращої швидкості, без зміни макета плати або вимог напруги.Це робить його найкращим вибором для критично важливих термінів конструкцій, що потребують більш швидкої реакції сигналу, залишаючись в межах одного і того ж проектного сліду.

EPM7192SQC160-15 етапів програмування

1. Введіть режим провайдера

Перший крок-перемикання пристрою в режим провайдера (програмування в системі).Це робиться через інтерфейс JTAG.Потрапивши в режим провайдера, всі шпильки вводу/виводу на пристрої розміщуються в безпечному режимі TRI-State, щоб запобігти непередбачуваному логічному перешкоді під час програмування.Ця ініціалізація, як правило, займає близько 1 мілісекунди.

2. Перевірте ідентифікатор пристрою

Унікальний ідентифікатор кремнію вбудований у пристрій, щоб перевірити, що це правильна модель до початку програмування.Система зміщується в інструкції з читання та отримує ідентифікатор через лінію TDO (випробування даних).Ця перевірка гарантує, що інструмент програмування підключений до правильного CPLD та уникає помилок, як перезапис іншої частини.

3. Основна стирання

Основна стирання очищає всі раніше збережені дані в пам'яті EEPROM про CPLD.Це готує мікросхему до отримання нової конфігурації.Команда стирання ініціює імпульс, який зазвичай триває близько 100 мілісекунд, забезпечуючи скидання всіх програмованих клітин.

4. Програма EEPROM

Нові дані конфігурації завантажуються в пристрій, зміщуючи адресу та біти даних через порт JTAG.Кожна комірка пам'яті записується по одному, з імпульсом програмування, застосованим після кожного успішного циклу запису.Цей процес визначає логічну структуру, яку CPLD використовуватиме під час живлення.

5. Перевірте EEPROM

Після програмування пристрій виконує крок перевірки.Це передбачає зчитування кожного запрограмованого місця пам'яті та порівняння вихідних значень проти передбачуваних даних.Якщо перевірка не вдається, процес повинен бути повторений.Цей крок гарантує, що конфігурація була успішно написана.

6. Вихід з режиму провайдера

Після завершення перевірки для виходу з режиму провайдера видається остаточна команда.Пристрій реактивує свої штифти вводу/виводу і поновлює нормальну роботу.Цей перехід також займає близько 1 мілісекунд і завершує цикл програмування в системі.

EPM7192SQC160-15 Розміри упаковки

• Розмір тіла: 28 мм × 28 мм

• Висота пакету: 3,4 мм

• Шпилька: 0,65 мм

EPM7192SQC160-15 Виробник

EPM7192SQC160-15 спочатку виготовляли Корпорація Altera, компанія, відома своїми вдосконаленими програмованими логічними пристроями.У 2015 році Altera придбала Корпорація Intel, і пристрій тепер є частиною групи програмованих рішень Intel у сімействі CPLD Max 7000S.Intel продовжує підтримувати Legacy Altera Products, хоча EPM7192SQC160-15 зараз класифікується як застарілий у більшості офіційних каталогів.Незважаючи на його припинену статус, історична репутація Intel над надійністю та спадщиною Altera у високоефективних логічних рішеннях забезпечують постійний попит та доступність через вторинні дистриб'ютори.

Висновок

EPM7192SQC160-15 є корисним і гнучким чіпом для обробки завдань цифрового управління у багатьох електронних системах.Він пропонує достатню логічну потужність для таких робочих місць, як створення власних державних машин, керування сигналами та з'єднання різних пристроїв.Він підтримує різні рівні напруги, працює на швидких швидкостях, і його можна легко оновлювати через JTAG.Його внутрішня конструкція дозволяє плавно потік сигналу та легкі зміни логіки.Незважаючи на те, що він зараз припиняється, це все ще чудовий варіант для старих або постійних проектів, і його можна замінити подібними мікросхемами, які пропонують швидшу або ширшу підтримку температури.

PDF -таблиця

EPM7192SQC160-15 DATESTES:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Чи можу я запрограмувати EPM7192SQC160-15, не видаляючи його з плати?

Так, мікросхема підтримує програмування в системі (ISP) через інтерфейс JTAG, тому ви можете програмувати або перепрограмувати його безпосередньо, поки він припаяться на друкованій платі, що спрощує оновлення дизайну та зменшує переробку.

2. Яке програмне забезпечення для програмування я повинен використовувати для EPM7192SQC160-15?

Ви можете використовувати програмне забезпечення Quartus II Altera (старіші версії) для створення логічних конструкцій, складання коду та управління процесом програмування на основі JTAG.Quartus II підтримує пристрої Max 7000S, такі як EPM7192SQC160-15.

3. Чи потрібна EPM7192SQC160-15 для роботи зовнішньої пам'яті?

Ні, він має внутрішню пам'ять конфігурації на основі EEPROM.Вся логічна конфігурація зберігається всередині мікросхеми, тому зовнішня пам'ять не потрібна для зберігання логічних станів або послідовностей завантаження.

4. Що робить EPM7192SQC160-15 придатним для промислового використання?

Його надійна операція 5В, багатовольтова сумісність вводу/виводу, швидка логічна обробка та неноматна пам'ять на основі ЕЕПРОМ роблять її надійною для промислових систем, які потребують стабільних та довговічних цифрових логічних функцій.

5. Як EPM7192SQC160-15 обробляє змішані системи напруги?

Завдяки підтримці багатовольтової вводу/виводу, пристрій може взаємодіяти як з рівнями 3,3 В та 5 В, що робить його ідеальним для систем змішаного сигналу та взаємодію з сучасними компонентами низької напруги.

Навіщо вибрати EPF10K100EFC484-3 для свого проекту

на 2025/06/13

Що таке SPST -перемикач і як він працює?

на 2025/06/12

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147760

-

USB-C Pinout та функції

на 2000/04/18 111969

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

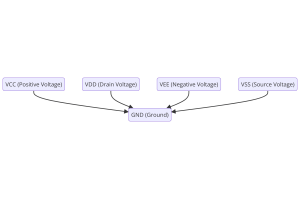

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83733

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79520

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66930

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63080

-

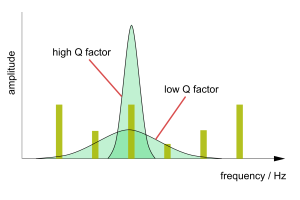

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63024

-

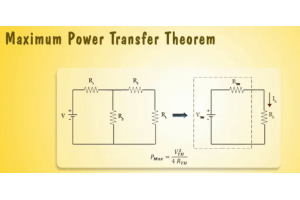

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54090

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52163