EPM7256SQC208-10 Посібник: Особливості, Покін, Програмування, програми та таблиця даних

Цей посібник стосується EPM7256SQC208-10, тип програмованого мікросхеми, виготовленого Intel (спочатку Altera).Він походить від сім'ї Max® 7000S і відомий тим, що він швидко, надійний та простий у програмі, поки він вже знаходиться всередині пристрою.Ця стаття пояснює, що робить чіп, як він працює, де він використовується, і чому це чудовий вибір, якщо вам потрібен сильний і гнучкий логічний пристрій для вашого проекту.Каталог

Огляд EPM7256SQC208-10

З EPM7256SQC208-10 є частиною сімейства Intel (раніше Altera) Max® 7000S, високоефективного діапазону CPLD, відомого своїми надійними можливостями програмування та логічної оптимізації.Ця модель може похвалитися близько 5000 корисних воріт і включає 256 макроцеллів, розміщених у 208-контактній пластиковій квадроциклій упаковці (PQFP).Він працює з частотою до 128,2 МГц і підтримує операційну напругу 5,0 В, з максимальною затримкою розповсюдження 7,5 нс та операційною температурною стелею +70 ° C.Ключовою особливістю є його програмування в системі через вбудовану IEEE STD.1149.1 Інтерфейс JTAG, що дозволяє динамічну конфігурацію.Пристрої MAX® 7000S виготовляються за допомогою розширеної технології CMOS, пропонуючи такі функції, як затримки логіки PIN-до шпильки, швидко, як 5 нс, і частоти зустрічі, що досягають до 175,4 МГц.Сім'я представляє різноманітні варіанти упаковки та розроблена з програмованими макроцеллами, що сприяють значній економії електроенергії за 50% зниження в деяких випадках.Крім того, він включає біт безпеки для захисту власних конструкцій.

Якщо вашій організації потрібне надійне програмоване логічне рішення, EPM7256SQC208-10 є надійним вибором, тому зв’яжіться з нами сьогодні, щоб забезпечити своє масове замовлення.

Моделі CAD EPM7256SQC208-10

EPM7256SQC208-10 Символ

EPM7256SQC208-10 Слід

EPM7256SQC208-10 3D-модель

EPM7256SQC208-10 Особливості

• Висока логічна щільність: EPM7256SQC208-10 забезпечує близько 5000 корисних воріт і містить 256 макроцелів.Ця висока логічна ємність робить її ідеальною для впровадження складних комбінаційних схем та ефективної логічної інтеграції в компактні конструкції.

• Швидка продуктивність: З максимальною робочою частотою 128,2 МГц та затримкою поширення всього 7,5 нс, цей CPLD забезпечує швидку обробку та швидкі часи реагування, добре для високошвидкісних застосувань.

• Програмність в системі (провайдер): Оснащений IEEE STD.1149.1 Інтерфейс JTAG, пристрій дозволяє проводити програмування та тестування в системі без необхідності фізичного видалення, полегшуючи ітеративну розробку та оновлення.

• Вдосконалена архітектура: Використовуючи максимальну архітектуру другого покоління Altera та виготовлений за допомогою вдосконаленої технології CMOS, EPM7256SQC208-10 пропонує підвищену продуктивність та довговічність, забезпечуючи надійність у різних оперативних умовах.

• Управління живленням: Пристрій має програмовані режими економії електроенергії, які можуть зменшити споживання електроенергії на понад 50% на макроцелл, підтримуючи енергоефективні конструкції та продовжуючи час роботи акумулятора в портативних додатках.

• Особливості безпеки: Програмований біт безпеки забезпечує захист від несанкціонованого доступу та копіювання власних конструкцій, ефективно захищаючи інтелектуальну власність.

• Широкі умови експлуатації: Працюючи при 5,0 В і здатні функціонувати при температурі до +70 ° C, цей CPLD адаптується до різноманітних екологічних умов, що робить його придатним як для промислових, так і для комерційних застосувань.

• Гнучкі стандарти вводу/виводу : Підтримує операції інтерфейсу Multivolt ™ вводу/виводу, сумісні з системами 3,3 В і 5,0 В.Ця гнучкість дозволяє безперебійній інтеграції з існуючим та новим обладнанням, зменшуючи складність та витрати системи.

• Підтримка дизайну: EPM7256SQC208-10 підтримується низкою інструментів дизайну та програмами обладнання, спрощенням процесу розробки та дозволяє зосередитись на інноваціях, а не на проблемах сумісності.

EPM7256SQC208-10 PINOUT Діаграма

Ця діаграма показує макет PIN-коду для мікросхеми EPM7256SQC208-10 від Altera.Чіп має 208 штифтів, розташованих з усіх чотирьох сторін у квадратній формі.Привок 1 починається в верхньому лівому куті, а цифри проходять навколо мікросхеми в напрямку проти годинникової стрілки, вниз по лівій стороні до шпильки 53, поперек нижньої частини до 105, вгору по правій стороні до шпильки 157 і назад до верхнього права.Мітки допомагають вам знати, з чого почати та як правильно розмістити мікросхему на платі.Назва в центрі "EPM7256E / EPM7256S" означає, що цей макет працює для обох версій чіпів.Ця діаграма важлива при підключенні ліній потужності, сигналів або програмування до мікросхеми.

EPM7256SQC208-10 Блок-схема

Блок-схема EPM7256SQC208-10 показує, як чіп організований для вирішення цифрових логічних завдань.У ньому є чотири основні логічні блоки під назвою Lab A, B, C і D. Кожен блок містить 16 макроцелів, які є основними частинами будівництва, які виконують логічну роботу.Так загалом, всередині мікросхеми є 64 макроцелі.Навколо цих логічних блоків є блоки управління вводу/виводу, які з'єднують мікросхему до зовнішнього світу через вхідні та вихідні шпильки.Кожен контрольний блок керує від 6 до 16 штифтів, відпускаючи сигнали, що входять або виходять з -за потреби.

У центрі знаходиться програмований масив взаємозв'язків (PIA), який діє як система шосе, дозволяючи сигналам рухатися між логічними блоками та шпильками вводу/виводу.Це дозволяє направляти дані будь -яким способом, необхідним для вашого дизайну.У верхній частині ліворуч на схемі відображаються деякі входи управління, такі як Global Clock (GCLK), Увімкнення виходу (OE) та Clear (GCLR).Ці сигнали допомагають керувати термінами та поведінкою логічних схем через мікросхему.

Технічні характеристики EPM7256SQC208-10

|

Тип |

Параметр |

|

Виробник |

Altera/Intel |

|

Серія |

Max® 7000s |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Програмований тип |

В системному програмованому |

|

Затримка часу TPD (1) Макс |

10 нс |

|

Постачання напруги - внутрішнє |

4,75 В ~ 5,25 В |

|

Кількість логічних елементів/блоків |

16 |

|

Кількість макроцелів |

256 |

|

Кількість воріт |

5000 |

|

Кількість вводу/виводу |

164 |

|

Робоча температура |

0 ° C ~ 70 ° C (TA) |

|

Монтажний тип |

Поверхневе кріплення |

|

Пакет / кейс |

208-BFQFP |

|

Пакет пристроїв постачальника |

208-PQFP (28x28) |

|

Базовий номер товару |

EPM7256 |

Програми EPM7256SQC208-10

Промислова автоматизація

EPM7256SQC208-10 широко використовується в системах промислової автоматизації.Його висока логічна щільність та швидка продуктивність забезпечують складні завдання управління, безперешкодно взаємодіючи з датчиками та приводами.Цей CPLD ідеально підходить для підвищення точності та ефективності виробничих ліній, систем управління процесами та робототехнічних програм.

Телекомунікації

У телекомунікаціях цей CPLD перевершує в управлінні потоком даних та цілісністю сигналу в мережах.Він підтримує такі функції, як перетворення сигналу, маршрутизація та обробка в комутаторах та маршрутизаторах, забезпечуючи надійну та ефективну комунікаційну інфраструктуру.

Автомобільні системи

У автомобільній промисловості цей пристрій сприяє надійності та витонченості таких систем, як підрозділи управління двигуном, інформаційно-розважальні системи та технології сприяння водіям.Його надійна продуктивність в різних умовах робить його придатним для критичних для безпеки застосувань.

Медичні пристрої

Точність та програмованість EPM7256SQC208-10 роблять його цінним у медичному обладнанні, де важливі точні контроль та надійна експлуатація.Він використовується в пристроях для моніторингу життєвих життєвих сил, управління діагностичними інструментами та автоматизації лікування лікування.

Аерокосмічна та оборона

У аерокосмічній та обороні EPM7256SQC208-10 використовується в системах, що потребують високого рівня надійності та продуктивності, таких як супутникові комунікації, навігаційні засоби та контроль військового обладнання.Його здатність діяти в екстремальних умовах корисна.

Навчальні та дослідницькі установи

Цей CPLD також популярний у навчальних умовах та дослідницьких проектах, де його перепрограмантність та гнучкість полегшують експерименти та навчання в цифровому дизайні та електроніці.Це дозволяє ефективно прототип та перевіряти різні логічні конструкції.

EPM7256SQC208-10 Подібні частини

EPM7256SQC208-10 етапи програмування

1. Введіть режим провайдера

Цей початковий крок важливий, оскільки він переходить CPLD від звичайного режиму експлуатації до режиму програмування в системі (ISP).Це досягається, надіславши певну команду через інтерфейс JTAG.Під час цього процесу всі шпильки вводу/виводу CPLD є тризначними (інвалідами), щоб уникнути будь-яких перешкод або конфліктів з іншими компонентами ланцюга.Перехід в режим провайдера готує пристрій для безпечного програмування і займає близько 1 мілісекунди.

2. Перевірте ідентифікатор

Потрапивши в режим провайдера, система виконує перевірку ідентифікатора, щоб переконатися, що правильний пристрій запрограмований.Це передбачає читання унікального ідентифікатора кремнію пристрою через інтерфейс JTAG.Цей крок хороший для перевірки того, що команди програмування та дані будуть надіслані на правильний пристрій, запобігаючи помилковому програмуванню та потенційному пошкодженню пристрою.

3. Основна стирання

Перш ніж нові дані можуть бути запрограмовані, існуючі дані в межах CPLD повинні бути стерті.Сума стирання етапів ефективно очищає всі програмовані клітини в пристрої.Це робиться шляхом зміщення в інструкції "Серти", а потім застосування 100-мілісекундного імпульсу, який стирає всю мікросхему.Цей крок важливий для того, щоб залишки попередніх конфігурацій не заважали новому програмуванню.

4. Програма

Цей крок включає фактичне програмування CPLD, де нові дані конфігурації записуються в пристрій.Дані та відповідні адреси зміщуються в пристрій через інтерфейс JTAG.Кожна пара адреси та даних вимагає імпульсу програмування, щоб переконатися, що дані правильно записуються в клітини, що не страждають полегшеною пам'яттю, CPLD.Цей крок повторюється для кожної точки даних через карту пам'яті пристрою.

5. Перевірте

Постпрограмування, потрібно перевірити, що дані були правильно записані на пристрій.Цей крок перевірки передбачає зчитування запрограмованих даних з кожної адреси та порівняння їх з вихідними вхідними даними.Цей крок забезпечує цілісність даних та підтверджує, що процес програмування був успішним без будь -яких помилок.

6. Вихід з режиму провайдера

Кінцевим кроком у процесі програмування є вихід із режиму провайдера та повернення CPLD у звичайний оперативний режим.Це робиться, надіславши іншу команду через інтерфейс JTAG.Після успішного виходу шпильки вводу/виводу реактивуються, і пристрій відновлює нормальну функцію.Цей крок, як правило, займає близько 1 мілісекунд.

Переваги EPM7256SQC208-10

НЕПРАВИТНА КОНФІГУРАЦІЯ

EPM7256SQC208-10 використовує технологію EEPROM, що дозволяє їй постійно зберігати конфігурацію.Цей ннометрачний характер означає пристрій не потрібно перезавантажувати дані його конфігурації із зовнішньої пам'яті кожного разу, коли він працює.Це призводить до більш швидкого часу запуску та скорочує загальну складність дизайну обладнання, усуваючи необхідність додаткових компонентів зберігання конфігурації.

Програмність в системі (провайдер)

Однією з особливостей видатних особливостей EPM7256SQC208-10 є його підтримка програмності в системі.Це дозволяє запрограмувати та перепрограмувати пристрій під час вбудованого в кінцевому застосуванні, не потребуючи фізичного видалення.Ця можливість спрощує оновлення та модифікації, забезпечуючи гнучкість та простоту використання під час розробки та протягом усього життєвого циклу продукту.

Висока кількість вводу/виводу та логічна щільність

Пристрій пропонує значну кількість логічних ресурсів та шпильок вводу/виводу, з 256 макроцелами та 164 штифтами вводу/виводу користувачів.Ця висока кількість вводу/виводу та логічна щільність забезпечують інтеграцію декількох функцій в єдину мікросхему, полегшуючи більш складні конструкції, зберігаючи простір на друкованій платі.Ця перевага корисна в додатках, де простір дошки має премію, і важлива багатофункціональність.

Швидка затримка штифта до шпильки

З максимальною затримкою штифта до шпильки всього 10 нс, EPM7256SQC208-10 може виконувати високошвидкісні логічні операції.Цей швидкий час реагування чудовий у програмах, які потребують швидкої можливості обробки, таких як швидкісні комунікації чи обчислення, гарантуючи, що система відповідає суворим критеріям продуктивності.

Широка сумісність напруги

EPM7256SQC208-10 розроблений таким чином, щоб бути гнучким з точки зору сумісності напруги, підтримуючи внутрішню роботу при рівні 5 В та вводу/виводу на 3,3 В. Ця можливість подвійної напруги дозволяє пристрою взаємодіяти з системами 3,3 В і 5 В, зменшуючи потребу в перекладах рівня напруги та спрощення системи системи.

EPM7256SQC208-10 Розміри упаковки

• Тип пакету: 208-BFQFP (пластиковий квадратичний пакет)

• Кількість шпильок: 208 ведучих

• Розмір тіла (l × w): 28 мм × 28 мм

• Стиль монтажу: Технологія поверхневого кріплення (SMT)

• Свинцева крок: Зазвичай 0,5 мм між шпильками (стандарт для BFQFP)

• Пакетний матеріал: Пластик

• Товщина упаковки: Приблизно 3,5 мм (незначно змінюється виробником)

• Теплові характеристики: Відсутність оголеної накладки;Стандартне розсіювання навколишнього середовища через дошку

• Упаковка лотка: Поставляється в лотках для обробки обсягу та автоматизації вибору та місця

EPM7256SQC208-10 Виробник

EPM7256SQC208-10 спочатку був розроблений та виготовлений Корпорація Altera, провідний піонер у програмованих логічних пристроях, відомі своєю серією CPLD Max® 7000s.У 2015 році Altera придбала Корпорація Intel, один з найбільших у світі виробників напівпровідників.З моменту придбання Intel продовжує підтримувати та інтегрувати технології CPLD та FPGA Altera в рамках своєї групи програмованих рішень.EPM7256SQC208-10 являє собою спадщину Intel у пропонуванні високоефективних, програмованих логічних рішень, пристосованих для широкого спектру промислових, телекомунікацій та вбудованих програм.Хоча зараз класифікується як застаріла, частина відображає давню прихильність Intel до надійних та гнучких програмованих логічних пристроїв.

Висновок

EPM7256SQC208-10-це розумний і надійний чіп, який допомагає зробити цифрові системи безперебійно.Він економить живлення, підтримує різні напруги та дозволяє програмувати її, поки він вже встановлений, що робить оновлення легкими.Незважаючи на те, що зараз це старший чіп, інші все ще використовують його, оскільки він добре працює у всіх видах систем.Якщо вам потрібна суцільна мікросхема для управління логікою у вашому дизайні, цей чудовий варіант.Зв’яжіться з нами сьогодні, якщо ви хочете замовити його оптом.

PDF -таблиця

EPM7256SQC208-10 DATASHEETS:

Програмний диск 06/листопад/2020.pdf

Циліндричні тримачі акумуляторів.pdf

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Які інструменти програмування сумісні з EPM7256SQC208-10?

Ви можете використовувати програмне забезпечення Quartus II Intel (раніше Altera Quartus), а також сумісний з JTAG-програміста, як USB-Blaster, для налаштування та програмування EPM7256SQC208-10 безпосередньо в системній системі.

2. Чи можу я перепрограмувати EPM7256SQC208-10 кілька разів?

Так, EPM7256SQC208-10 підтримує кілька циклів перепрограмування, використовуючи програму в системі на основі EEPROM, що робить його ідеальним для ітеративної розробки дизайну або оновлень після розгортання.

3. Чи може epm7256sqc208-10 обробляти суворі умови експлуатації?

Він надійно працює в межах комерційного температурного діапазону від 0 ° C до +70 ° C, що достатньо для більшості промислових та вбудованих застосувань, хоча і не для екстремальних або автомобільних середовищ.

4. Чи можу я все-таки програмувати EPM7256SQC208-10, не видаляючи його з плати?

Так.Чіп підтримує програму в системі (ISP) через JTAG, що дозволяє перепрограмувати його, поки він уже спалений на вашій дошці, заощаджуючи час та зусилля під час розробки чи обслуговування.

5. Що робить EPM7256SQC208-10 кращим, ніж стандартний мікроконтролер для логічних завдань?

На відміну від мікроконтролерів, EPM7256SQC208-10-це CPLD, який переважає при виконанні паралельних логічних операцій з точними термінами.Це ідеально, коли вам потрібен швидкий, детермінований цифровий контроль над декількома сигналами.

Теореми Деморгана пояснили: спрощення логічних виразів для кращої конструкції ланцюга

на 2025/04/25

Приклади теореми та схеми Нортона

на 2025/04/24

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147776

-

USB-C Pinout та функції

на 2000/04/18 112022

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

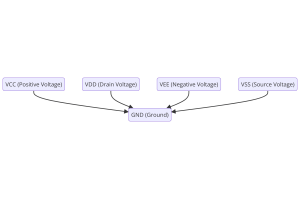

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83777

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79577

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66964

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63104

-

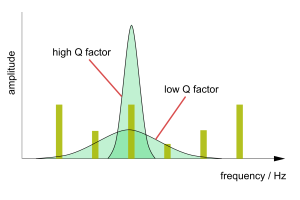

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63041

-

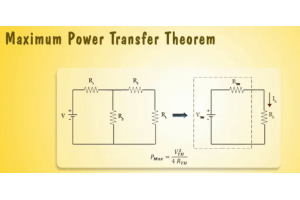

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54097

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52190