Огляд FPGA LFEC3E-3Q208C: функції, програми, програмування та технічні характеристики

У цій статті ви дізнаєтесь про LFEC3E-3Q208C, FPGA від напівпровідника решітки.Ви побачите, що це таке, основні функції, які він пропонує, і чому це корисно для багатьох дизайнів середнього класу.Вміст також проводить вас через його технічні характеристики, програми та покроковий процес програмування, а також деталі про плюси, мінуси та виробник.Каталог

Що таке LFEC3E-3Q208C?

З LFEC3E-3Q208C є економічно ефективним польовим запрограмованим масивом воріт (FPGA) від напівпровідника решітки, розробленого в рамках сім'ї Latticeec (економіки).Ця родина була розроблена для надання програмованих логічних рішень, які балансують доступність з надійною продуктивністю для основних конструкцій.В рамках ієрархії Latticeec він сидить у середині діапазону, пропонуючи близько 3000 логічних елементів та ефективне використання електроенергії, подолавши розрив між меншими пристроями введення та більшою, більш інтенсивною ресурсною моделями.Більш широка серія LatticeECP/EC підкреслює недорогу програму, масштабованість та гнучкість у різних розмірах пристроїв, коли варіант ЄС зосереджується на ефективності, керованої економікою.

Шукаєте LFEC3E-3Q208C?Зверніться до нас, щоб перевірити поточні акції, час виконання та ціни.

Особливості LFEC3E-3Q208C

• Логічні ресурси

Пристрій інтегрує близько 3100 логічних елементів, організованих у 384 блоки, надаючи йому достатню ємність для конструкцій середнього класу.Цей баланс ресурсів робить його придатним для контрольної логіки, обробки сигналів та вбудованих додатків без надмірних витрат.

• Програмований ввод/ви

З 145 програмованими вхідними/вихідними шпильками він підтримує широкий спектр варіантів підключення.Ці вводу/ОС сумісні з декількома стандартами, такими як LVCMOS, LVTTL, LVDS, PCI та SSTL, що забезпечує гнучку інтеграцію системи.

• Вбудована пам'ять

FPGA включає спеціалізовану оперативну пам’ять (EBR) та розподілені ресурси оперативної пам’яті, забезпечуючи ефективне зберігання мікросхем.Це дозволяє реалізувати буферизацію даних, таблиці пошуку або невеликі вбудовані спогади безпосередньо всередині пристрою.

• Управління годинником

Він має до чотирьох інтегрованих PLL, пропонуючи частоту множення, поділ та зміну фаз.Це дозволяє точного контролю часу та синхронізації для високошвидкісних конструкцій.

• Підтримка пам'яті DDR

Пристрій включає апаратну підтримку інтерфейсів DDR, здатних запускати DDR400 (200 МГц).Це робить його практичним для конструкцій, які потребують зовнішнього високошвидкісного доступу до пам'яті.

• Ефективність потужності

Працюючи з основним постачанням 1,2 В, FPGA мінімізує загальне споживання електроенергії.Його дизайн з низькою потужністю ідеально підходить для портативних або енергоглутувальних додатків.

• Особливості на рівні системи

Вбудовані функції, такі як IEEE 1149.1 Граничне сканування, Логічний аналіз на мікросхемі (ISPracy) та інтерфейс спрощення спрощення SPI Boot Flash.Ці функції скорочують час розробки та підвищують надійність дизайну.

• Підтримка розвитку

Підтримується дизайнерським номером iSplever, пристрій виграє від автоматизованого синтезу, місця та інструментів перевірки.Ви також можете використовувати IP-блоки ISPLEVERCORE для прискорення загальних функцій та скорочення часу на ринок.

Діаграма сімейства LatticeECP/EC

Блок-схема сімейства LatticeECP/EC (включаючи LFEC3E-3Q208C) показує, як будується FPGA та як його деталі працюють разом.Програмовані клітини вводу/виводу (фотографії) розміщуються по краях для з'єднання мікросхеми із зовнішніми пристроями, підтримуючи багато стандартів сигналу.Всередині програмовані функціональні одиниці (PFUS) обробляють логічні операції, з деякими парними до вбудованого блоку оперативної пам’яті (EBR) для зберігання даних та інших орієнтованих лише на логіку.Sysclock PLL керує сигналами годинника, щоб конструкція могла працювати з правою швидкістю та термінами.Порт SysConfig та порт JTAG дозволяють вам легко програмувати, тестувати та налагодити FPGA.Цей макет дає гнучкість LFEC3E-3Q208C, надійну продуктивність та просту інтеграцію в конструкції, чутливі до витрат.

Діаграма шматочків LatticeECP/EC

Шматочок у сімействі LatticeECP/EC, як і в LFEC3E-3Q208C, є основним логічним блоком, який поєднує блоки LUT4 та перенесення для виконання логічних та арифметичних операцій.Кожен шматочок також включає шльопанці/засувки для зберігання даних та ввімкнення послідовної логіки, з мультиплексорами для маршруту сигналів гнучко або через регістри, або безпосередньо.Ця структура важлива, оскільки вона надає швидкість, гнучкість та ефективність FPGA для обробки як простих, так і складних цифрових конструкцій.Наступна таблиця узагальнює описи сигналів зрізів, включаючи їх функції, типи, назви сигналів та цілей.

|

Функціонування |

Тип |

Назви сигналу |

Опис |

|

Введення |

Сигнал даних |

A0, B0, C0, D0 |

Входи до LUT4 |

|

Введення |

Сигнал даних |

A1, B1, C1, D1 |

Входи до LUT4 |

|

Введення |

Багатоземний |

M0 |

Багатоцільовий вхід |

|

Введення |

Багатоземний |

М1 |

Багатоцільовий вхід |

|

Введення |

Контрольний сигнал |

CE |

Увімкнути годинник |

|

Введення |

Контрольний сигнал |

LSR |

Місцевий набір/скидання |

|

Введення |

Контрольний сигнал |

Клиновий |

Системний годинник |

|

Введення |

Інтер-PFU-сигнал |

Fcin |

Швидке перенесення в¹ |

|

Випуск |

Сигнали даних |

F0, F1 |

LUT4 Вихідні обхідні сигнали |

|

Випуск |

Сигнали даних |

Q0, Q1 |

Зареєструйте результати |

|

Випуск |

Сигнали даних |

Ofx0 |

Вихід LUT5 MUX |

|

Випуск |

Сигнали даних |

Ofx1 |

Вихід LUT6, LUT7, LUT8 2 MUX залежно від шматочка |

|

Випуск |

Інтер-PFU-сигнал |

FCO |

Для правильного PFU швидкий вихід ланцюга переносу¹ |

Технічні характеристики LFEC3E-3Q208C

|

Тип |

Параметр |

|

Виробник |

Ґратний напівпровідник |

|

Напруга - постачання |

1,14v ~ 1,26 В |

|

Загальні шматочки оперативної пам’яті |

56,320 |

|

Пакет пристроїв постачальника |

208-PQFP (28x28) |

|

Серія |

ЄК |

|

Пакет / кейс |

208-BFQFP |

|

Пакет |

Лоток |

|

Робоча температура |

0 ° C ~ 85 ° C (TJ) |

|

Кількість логічних елементів/клітин |

3100 |

|

Кількість вводу/виводу |

145 |

|

Монтажний тип |

Поверхневе кріплення |

|

Базовий номер товару |

Lfec3 |

Програми LFEC3E-3Q208C

1. Вбудовані системи управління

LFEC3E-3Q208C добре підходить для вбудованих контролерів на пристроях, промислова автоматизація та шлюзи IoT.Його помірна логічна щільність та недорога конструкція дозволяють замінити логіку фіксованої функції на програмовану гнучкість.Це полегшує модернізацію систем або адаптації до стандартів, що розвиваються, без переробки обладнання.

2. ДДР -пам’ять взаємозв'язок

Завдяки вбудованій підтримці пам'яті DDR400, пристрій може керувати буферизацією даних, журналами або тимчасовим зберіганням у програмах.Ця функція корисна в системах, де важлива швидкість зовнішньої пам'яті, але повна висока продуктивність FPGA не потрібна.Багато хто виграє від балансу швидкості, вартості та ефективності пам'яті.

3. Перетворення вводу/виводу мости та протоколу

Завдяки широкій підтримці стандартів вводу/виводу, таких як LVCMOS, LVTTL, LVDS, PCI та SSTL, FPGA ефективно для подолання різних цифрових інтерфейсів.Він може бути налаштований для перекладу сигналів між підсистемами, що робить його цінним у змішаних технологіях.Ця гнучкість допомагає продовжити термін експлуатації існуючого обладнання, забезпечуючи сумісність з новими компонентами.

4. Промислові та інфраструктурні програми

Пристрій також може служити в галузі промислового та інфраструктурного обладнання, що чутливого до витрат, де достатньо надійності та помірних продуктивності.Його підтримка прикордонного сканування, налагодження на мікросхемі та експлуатації з низькою потужністю робить його ідеальним для систем, які вимагають ефективності та легкого обслуговування.Типові ролі включають блоки управління, модулі інтерфейсу та системи моніторингу.

LFEC3E-3Q208C Подібні частини

|

Специфікація |

LFEC3E-3Q208C |

Lfec3e-3q208i |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

Логічні елементи (LUTS) |

~ 3,1K |

~ 3,1K |

~ 3,1K |

~ 3,1K |

~ 1,5 К |

~ 6,1k |

|

Логічні блоки |

384 |

384 |

384 |

384 |

192 |

768 |

|

Вбудований блок оперативної пам’яті (EBR) |

~ 55 кб |

~ 55 кб |

~ 55 кб |

~ 55 кб |

~ 18 кб |

~ 92 кб |

|

Максимальна частота роботи |

~ 340 МГц |

~ 340 МГц |

~ 340 МГц |

~ 340 МГц |

~ 300 МГц |

~ 340 МГц |

|

Вводу/вир |

145 |

145 |

145 |

145 |

112 |

145 |

|

Пакет |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

|

Основна напруга |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

|

Діапазон температури |

0 ° C до +70 ° C |

–40 ° C до +85 ° C |

0 ° C до +70 ° C |

0 ° C до +70 ° C |

0 ° C до +70 ° C |

0 ° C до +70 ° C |

|

Дотримання / тип пакету |

Стандартний |

Промисловий |

Без свинцю (QN) |

Варіант (q) |

Стандартний |

Стандартний |

|

Застосування |

Середня щільність, загальний призначення |

Те саме, що і lfec3e, але промислове використання |

Те саме, що і lfec3e, але сумісна з упаковкою |

Та сама родина, легка міграція |

Варіант вартості низької щільності |

Оновлення більш високої щільності |

Етапи програмування LFEC3E-3Q208C

Перш ніж розпочати програмування LFEC3E-3Q208C, важливо підготувати правильні інструменти та зрозуміти потік дизайну до конфігурації пристрою.Кожен крок будує на попередньому, тому ретельна увага забезпечить плавний процес програмування.

1. Підготуйте обладнання та програмне забезпечення програмування

Ви починаєте з встановлення алмазного програміста ґратки або системи ISPVM, які є офіційними інструментами для цієї FPGA.Потім встановіть кабель програмування JTAG, такий як HW-USBN-2B, і переконайтеся, що драйвери належним чином встановлені.Цей крок гарантує, що ваш комп'ютер готовий спілкуватися з цільовим пристроєм без помилок з'єднання.

2. Реалізуйте свій дизайн у програмному забезпеченні розробки

Далі створіть новий проект у ґратному алмазі та виберіть LFEC3E-3Q208C як свій цільовий пристрій.Потім ви додаєте вихідні файли Verilog або VHDL, застосовуєте призначення PIN -адреси та визначаєте обмеження в терміни.Після того, як це буде зроблено, ви синтезуєте дизайн, виконуєте місце та маршруту і, нарешті, генеруєте файл Bitstream (.bit або .jed), який буде використовуватися для програмування.

3. Налаштуйте плату та з'єднання

Тепер підключіть кабель JTAG до дошки FPGA, переконавшись, що з'єднання заземлення надійне перед тим, як приєднати сигнальні лінії.Переконайтеся, що резистори, що підтягуються та знижують, правильно на місці, особливо на лініях TCK та відкритих.Якщо ваша плата має додаткові шпильки для управління, такі як Erase або ISPEN, вам потрібно належним чином налаштувати їх, щоб запобігти випадковому скиданнях під час програмування.

4. Програмуйте пристрій

За допомогою готового обладнання запустіть інструмент програмування та виберіть підключений кабель.Завантажте створений файл Bitstream і виберіть відповідний режим, як правило, JTAG, залежно від вашої установки.Запустіть процес програмування, і інструмент налаштує FPGA, перевіряючи, що дані були правильно записані.

5. Перевірте та налагоджуйте конфігурацію

Після програмування перевірте готові або ініціативні штифти на вашій дошці, щоб підтвердити, що FPGA успішно налаштувалася.Якщо потрібно, використовуйте логічний аналізатор ISPracy або прикордонні функції сканування для тестування функціональності та підтвердження поведінки сигналу.Ви можете повторити цикл дизайну та програмування, коли потрібні зміни, гарантуючи, що ваш проект вдосконалюється поетапно.

LFEC3E-3Q208C Переваги та недоліки

Переваги

• Низьке споживання електроенергії, що підходить для енергозахисних конструкцій

• економічно вигідно порівняно з FPGA вищого класу

• Простий ланцюг інструментів з легшою кривою навчання

• Поле налаштовує для оновлень після розгортання

• Компактний пакет з хорошим балансом ресурсів

Недоліки

• Обмежена продуктивність порівняно з більшими FPGA

• Нижня логіка та ємність пам'яті, ніж пристрої високого класу

• Менше сторонніх IP-ядер та підтримки екосистеми

• Міністерство інструментів не вистачає вдосконалених особливостей основних постачальників

• Не підходить для ультра-швидкісних інтерфейсів

Розміри упаковки LFEC3E-3Q208C

|

Тип |

Параметр |

|

Тип пакету |

208-PQFP (пластиковий квадратичний пакет) |

|

Розмір тіла |

28 мм × 28 мм |

|

Стовп |

0,5 мм |

|

Висота упаковки (макс) |

~ 3,4 мм |

|

Підряд |

208 шпильок |

|

Стиль пакету |

Крила для чайок (квадроцикл) |

|

Монтажний тип |

Поверхневе кріплення |

|

Код справи |

BFQFP-208 |

|

Пакет постачальників |

Лоток |

Виробник LFEC3E-3Q208C

LFEC3E-3Q208C виробляється Корпорація гратів , американська компанія зі штаб-квартирою в Хіллсборо, штат Орегон.Заснована в 1983 році, ґрата спеціалізується на розробці низької потужності, економічно ефективних польових програмних воріт (FPGA) та пов'язаних з ними рішень.Компанія зосереджується на включенні додатків на комунікаціях, обчислювальній службі, побутовій електроніці, промисловому та автомобільному ринках.Відомий своїм інноваціям в енергоефективних програмованих пристроях, ґрата зареєструвалася як ключовий гравець у галузі FPGA, особливо для проектів, які вимагають факторів компактних форм, зменшення споживання електроенергії та високої надійності.

Висновок

LFEC3E-3Q208C пропонує хорошу суміш низької вартості, низької потужності та достатньої логіки та пам'яті для проектів середнього класу.Він підтримує багато стандартів вводу/виводу, має вбудовану оперативну пам’ять та PLL, і може працювати з пам'яттю DDR400, що робить її корисною для управління, інтерфейсу та промислових завдань.Програмування просте з ґратними інструментами, а додаткові функції налагодження допомагають у тестуванні.Незважаючи на те, що він не може відповідати швидкості та ємності більших FPGA, це надійний вибір для конструкцій, які потребують гнучкості, ефективності та доступної продуктивності.

PDF -таблиця

LFEC3E-3Q208C DATESTES:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Чи підтримує високошвидкісні інтерфейси LFEC3E-3Q208C, такі як PCIE або Gigabit Ethernet?

Ні. LFEC3E-3Q208C призначений для мейнстріму та додаткових витрат, тому він не включає нативні високошвидкісні серійні приймачі.Натомість він фокусується на паралельних інтерфейсах та підтримці пам'яті DDR.

2. Чи можна перепрограмувати LFEC3E-3Q208C після розгортання?

Так.Як FPGA, LFEC3E-3Q208C повністю налаштований, що дозволяє оновлювати та модифікації дизайну навіть після розгортання.Ця гнучкість знижує довгострокові витрати на обслуговування та розширює життєві цикли продукції.

3. Як LFEC3E-3Q208C обробляє налагодження та тестування?

Пристрій інтегрує прикордонне сканування (IEEE 1149.1), логічний аналіз на мікросхемі (ISPracy) та підтримка спалаху SPI Boot.Ці вбудовані інструменти спрощують налагодження та зменшують потребу у зовнішньому апаратному забезпеченні.

4. Чи може LFEC3E-3Q208C розширити термін експлуатації старих апаратних систем?

Так, завдяки широким можливостям сумісності вводу/виводу та протоколу, він може взаємодіяти з старими системами з новими компонентами, допомагаючи бізнесу розширювати корисність існуючого обладнання.

5. Які інструменти програмування потрібні для LFEC3E-3Q208C?

Він запрограмований за допомогою алмазного програміста ґратки або системи ISPVM.Ці інструменти підтримують запис дизайну, генерацію Bitstream та конфігурацію пристроїв, що робить робочий процес упорядкованим.

AD73311LARS: PASHEET, функції, Посібник з розпилення та програмування

на 2025/08/28

EPM1270F256C4N MAX II CPLD Огляд: Особливості, технічні характеристики та додатки

на 2025/08/28

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/19 147782

-

USB-C Pinout та функції

на 2000/04/19 112070

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/19 111352

-

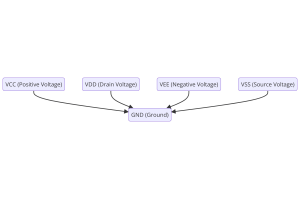

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/19 83829

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79641

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 67006

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63131

-

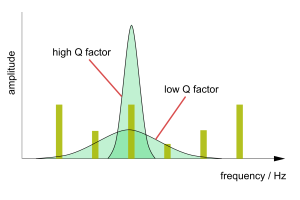

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63067

-

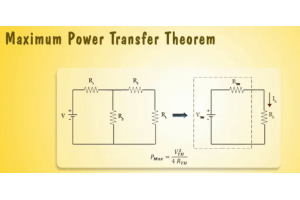

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54097

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52225