Решітка LFEC3E-3QN208C FPGA Посібник: Особливості, таблиця та альтернативи

Якщо ви працюєте над проектами, які потребують надійного контролю логіки без перегляду бюджету, FPGA LFEC3E-3QN208C варто знати.Це дає вам правильну суміш логіки, пам'яті та гнучкості вводу/виводу в компактному пакеті.У цьому посібнику ви побачите його основні функції, як він працює всередині, де ви можете ним користуватися, як його програмувати та які переваги та обмеження очікувати.Каталог

Що таке LFEC3E-3QN208C?

З LFEC3E-3QN208C є пристроєм FPGA від сім’ї EC/EC/ECP Supsice, розробленого як частина програмованої логічної серії компанії з економічного класу.Цей пристрій пропонує масштабовану архітектуру цифрової логіки.Суфікс "QN208C" ідентифікує свій компактний 208-контактний пакет, що робить його придатним для інтеграції, де простір дошки викликає занепокоєння.Як член зрілої родини Latticeec/ECP, він має ознаки гнучкості та надійного дизайну, знайденого в цій лінійці продуктів.

Шукаєте LFEC3E-3QN208C?Зверніться до нас, щоб перевірити поточні акції, час виконання та ціни.

Особливості LFEC3E-3QN208C

• Логічна здатність

LFEC3E-3QN208C забезпечує близько 3100 логічних елементів, які можуть бути використані для реалізації цифрових схем, державних машин та спеціальних даних.Цей рівень щільності підходить для конструкцій середнього класу, таких як комунікаційні інтерфейси, промисловий контроль та вбудована обробка.

• Пам'ять на мікросхемі

Він інтегрує близько 56,320 біт блокованої оперативної пам’яті та розподілену оперативну пам’ять, що дозволяє зберігати буфери даних, таблиці пошуку або невеликі FIFOS безпосередньо всередині FPGA.Це зменшує залежність від зовнішньої пам'яті для багатьох завдань даних помірного розміру.

• Ресурси вводу/виводу

Розміщений у пакеті QFP 208-контактний, пристрій підтримує близько 140+ штифтів вводу/виводу користувачів залежно від конфігурації.Це робить його гнучким для додатків, що потребують декількох інтерфейсів, паралельних автобусів або підключення до змішаного сигналу.

• Робоча напруга

Основа працює приблизно в 1,2 В, при цьому банки вводу/виводу підтримують декілька стандартів напруги від 1,2 В до 3,3 В. Ця широка сумісність дозволяє FPGA взаємодіяти як із сучасною логікою низької напруги, так і з застарілими системами 3,3 В.

• Система

Пристрій включає PLL на мікросхемі (Sysclock ™), які можуть розмножуватися, розділити або фазові вхідні годинники.Це дозволяє генерувати точні внутрішні годинники для інтерфейсів DDR, швидкісних шляхів даних та синхронізованих логічних доменів.

• Підтримка інтерфейсу пам'яті

LFEC3E-3QN208C підтримує інтерфейси DDR SDRAM аж до DDR-400 (тактового годин).Це дає йому можливість безпосередньо підключатися до зовнішніх мікросхем пам'яті для зберігання або буферизації більш високої ємності в додатках.

• Стандарти вводу/виводу

Він підтримує широкий спектр стандартних протоколів сигналізації в галузі, включаючи LVCMOS, LVTTL, SSTL, HSTL, PCI та LVDS.Це забезпечує сумісність із широким набором процесорів, ASIC та комунікаційних інтерфейсів.

• Програмність в системі

FPGA можна запрограмувати через JTAG (IEEE 1149.1) та підтримує реконфігурацію в системі.Це робить розробку, налагодження та оновлення поля прямого, не видаляючи пристрій з друкованої плати.

• Налагодження та аналіз

Він забезпечує підтримку логічного аналізатора ISPracy Lattice, який досліджує внутрішні сигнали у часі.Ця функція спрощує налагодження складних логічних конструкцій без необхідності зовнішніх зондів.

• Статус життєвого циклу

LFEC3E-3QN208C належить до родини ґратних ЕК, яка зараз вважається зрілою або припиненою лінійкою продуктів.

Блок -схема Latticeec

Блок-схема сімейства FPGA Latticeec (наприклад, LFEC3E-3QN208C) показує, як організована його внутрішня архітектура для балансу логіки, пам'яті та підключення.По краях є програмовані клітини вводу -виводу (фотографії), які обробляють спілкування із зовнішніми пристроями та підтримують декілька стандартів напруги для гнучкого взаємозв'язку.Всередині сітка наповнена програмованими функціональними одиницями (PFU), де реалізована логіка користувачів, тоді як спеціалізовані вбудовані блок-барани (EBRS) забезпечують високошвидкісну пам'ять для буферизації та зберігання даних.Системні ресурси включають Sysclock PLL, які керують генерацією та синхронізацією годин, забезпечуючи стабільну високоефективну операцію, та порти SysConfig/JTAG, які дозволяють програмувати та тестування в системній системі.Ця композиція робить універсальну універсальну, поєднуючи переконавену логіку, вбудовану пам'ять та надійну введення/вивод для широкого спектру додатків у комунікаціях, контролі та вбудованих системах.

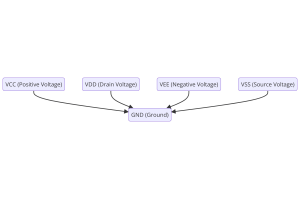

Діаграма банків Latticeec

Діаграма банків Latticeec для таких пристроїв, як LFEC3E-3QN208C, ілюструє, як шпильки вводу/виводу FPGA організовуються у вісім банків, кожен з яких має власні напруги живлення та еталон.Кожен банк може працювати самостійно через свій VCCIO шпильки, що дозволяють FPGA підтримувати кілька стандартів напруги вводу/виводу (наприклад, 1,2 В, 1,8 В, 2,5 В або 3,3 В) одночасно.Кожен банк також включає VРеф Шпильки, які чудово підходять для певних стандартів, таких як SSTL та HSTL, які потребують опорних напруг для встановлення належних логічних порогів.Ця модульна структура надає гнучкість інтерфейсу FPGA з різними зовнішніми компонентами, такими як процесори, пам'ять та периферійні пристрої без рівня.Банкована архітектура підвищує універсальність продукту і полегшує інтеграцію в системи змішаної напруги, що є ключовою перевагою у промислових та комунікаційних додатках.

Технічні характеристики LFEC3E-3QN208C

|

Тип |

Параметр |

|

Виробник |

Корпорація гратів |

|

Серія |

ЄК |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Кількість логічних елементів/клітин |

3100 |

|

Загальні шматочки оперативної пам’яті |

56,320 |

|

Кількість вводу/виводу |

145 |

|

Напруга - постачання |

1,14v ~ 1,26 В |

|

Монтажний тип |

Поверхневе кріплення |

|

Робоча температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / кейс |

208-BFQFP |

|

Пакет пристроїв постачальника |

208-PQFP (28 × 28) |

|

Базовий номер товару |

Lfec3 |

Програми LFEC3E-3QN208C

1. Вбудовані системи управління

LFEC3E-3QN208C може слугувати центральним логічним контролером у системах промислової автоматизації, робототехніки або моторного управління.Його перепрограмована архітектура дозволяє впроваджувати спеціальні машини та критичні за часом логіки без перепроектування обладнання.Завдяки низькій основній напрузі та декількома банками вводу/виводу, вона безперешкодно інтегрується як із сучасними датчиками, так і з традиційними контролерами.Це робить його ідеальним для надійних, вбудованих у часі управління рішеннями.

2. Перехід інтерфейсу мостового / протоколу

Оскільки FPGA підтримує декілька стандартів вводу/виводу та рівня напруги, він може слугувати мостом між різними протоколами зв'язку.Наприклад, він може перекладатися між застарілими автобусами (такими як PCI або паралельні інтерфейси) та новішими стандартами, такими як LVDS або DDR -пам'ять.Ця здатність допомагає продовжити термін експлуатації існуючих систем, дозволяючи інтеграцію нових пристроїв.Така гнучкість зменшує потребу у зовнішній логіці клею та прискорює інтеграцію системи.

3. Обробка сигналів у комунікаціях

LFEC3E-3QN208C здатний виконувати основні завдання DSP, включаючи фільтрацію, виявлення помилок або обробку пакетів у системах зв'язку.Його вбудований блок оперативної пам’яті та логічні клітини забезпечують ефективні ресурси для буферизації та управління потоками даних.Вивантажуючи ці функції з мікропроцесора, загальна пропускна здатність системи та чутливість покращуються.Це робить його придатним для бездротових модулів, дрібних базових станцій та мережевого обладнання.

4. Тест, вимірювання та приладобудування

У тестовій та вимірювальній техніці, такому як осцилоскопи, реєстратори даних або логічні аналізатори, FPGA може бути налаштована для зйомки, фільтрації та попередніх даних.Його програмовані банки вводу/виводу дозволяють безпосередньо підключити до різних рівнів сигналу без додаткової схеми перетворення.Використовуючи вбудовану оперативну пам’ять, тимчасові дані можна ефективно зберігати та переадресувати у зовнішні процесори.Ця здатність підвищує точність та знижує затримку в приладобувних додатках.

5. Прототипування та власні апаратні прискорювачі

Пристрій також може служити платформою для апаратного прототипування або дрібних прискорювачів.Він може реалізувати блоки шифрування, генератори контрольних суми або інші обчислювальні завдання безпосередньо в логіці.Це скорочує цикл розвитку порівняно з ASIC та забезпечує швидкі модифікації в цій галузі.Для досліджень, стартапів та на замовлення вбудованих рішень він пропонує економічно ефективну точку входу в прискорення на основі FPGA.

LFEC3E-3QN208C Подібні частини

|

Специфікація |

LFEC3E-3QN208C |

Lfec3e-3qn208i |

Lfec3e-3q208i |

LFEC3E-3TN100C |

LFEC3E-3TN144C |

LFEC3E-3FN256C |

|

Логічні елементи / клітини |

3100 |

3100 |

3100 |

3100 |

3100 |

3100 |

|

Вбудована пам'ять (шматочки) |

56,320 |

56,320 |

56,320 |

56,320 |

56,320 |

56,320 |

|

Максимальна частота роботи |

~ 340 МГц |

~ 340 МГц |

~ 340 МГц |

~ 340 МГц |

340 МГц |

340 МГц |

|

Кількість I/OS |

145 |

145 |

145 |

~ 80–90 |

97 |

160 |

|

Діапазон основної напруги |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

|

Робоча температура |

0 ° C до 85 ° C |

0 ° C до 85 ° C |

0 ° C до 85 ° C |

0 ° C до 85 ° C |

0 ° C до 70 ° C |

0 ° C до 85 ° C |

|

Тип пакету |

208-контактний QFP |

208-контактний QFP |

208-контактний QFP |

100-контактний TQFP |

144-контакт TQFP |

256-м'яч BGA |

|

Статус життєвого циклу |

Застарілий |

Застарілий |

Застарілий |

Застарілий |

Застарілий |

Застарілий |

|

Підтримувані стандарти вводу/виводу |

LVCMOS, LVTTL, LVDS, SSTL, HSTL, PCI |

Однаковий |

Однаковий |

Обмежений (менше банків) |

Той же набір, менше шпильок |

Повний набір з більшою кількістю банків |

|

Зовнішня підтримка пам'яті |

DDR до DDR-400 |

DDR до DDR-400 |

DDR до DDR-400 |

DDR до DDR-400 |

DDR до DDR-400 |

DDR до DDR-400 |

Етапи програмування LFEC3E-3QN208C

Перш ніж використовувати LFEC3E-3QN208C FPGA, вам потрібно запрограмувати його зі своїм спеціальним дизайном.Процес передбачає створення вашої логічної конструкції, генерування бітового потоку та перенесення його в мікросхему через підтримувані інтерфейси.

1. Дизайн та генерація біцтрамів

Ви починаєте з написання свого дизайну на HDL (Verilog або VHDL), а потім складайте його за допомогою інструментів розробки решітки, таких як Isplever або Diamond.Під час цього процесу ви будете синтезувати логіку, виконувати розміщення та маршрутизацію та застосовувати обмеження вводу/виводу та термінів.Потім інструмент створює файл Bitstream (.bit або .jed), який містить усі дані конфігурації, необхідні FPGA.Цей файл - це те, що ви пізніше перенесете в пристрій, щоб втілити свій дизайн у життя.

2. Виберіть режим конфігурації

Далі ви повинні вирішити, як FPGA завантажить свою конфігурацію.LFEC3E-3QN208C підтримує кілька режимів, таких як програмування JTAG для прямого завантаження або режими SysConfig, таких як послідовне або паралельне завантаження із зовнішньої флеш-пам'яті.Ви вибираєте режим, встановивши конфігураційні штифти пристрою (CFG [2: 0]) або шляхом проведення його належним чином до зовнішньої пам'яті.Вибір правильного режиму залежить від того, чи хочете ви швидке прототипування чи постійну конфігурацію живлення.

3. Підключіть інтерфейс програмування

Вибравши режим, ви підключаєте належне обладнання для програмування.Для JTAG ви будете використовувати кабель завантаження або програміст, пов'язаний з шпильками JTAG FPGA.Якщо ви використовуєте sysconfig, зовнішній спалах або мікроконтролер буде виступати джерелом конфігурації.Забезпечення належної проводки, призначення PIN -коду та послідовності живлення на цьому етапі корисно для надійного програмування.

4. Завантажте конфігурацію

З обладнанням на місці ви переносите Bitstream у FPGA.Програміст надсилає дані через інтерфейс JTAG або SYSCONFIG, а FPGA записує їх у свою внутрішню пам'ять конфігурації.Під час цього процесу пристрій перевіряє цілісність даних, використовуючи CRC та сигналізує про успіх, стверджуючи готовий штифт.У цей момент ваша конструкція стає активною, і FPGA починає працювати, коли ви його запрограмували.

5. Час виконання та реконфігурація

Нарешті, у вас є можливість перенастроювати пристрій, не видаляючи його з системи.Використовуючи JTAG або SysConfig, ви можете оновити FPGA новим Bitstream, якщо ваша конструкція зміниться.Ця здатність корисна для оновлення поля або ітеративного тестування.Скориставшись програмованою в системі, ви гарантуєте, що ваш LFEC3E-3QN208C може адаптуватися до вимог, що розвиваються з часом.

LFEC3E-3QN208C Переваги та недоліки

Переваги

• Недостатня опція FPGA для бюджетних конструкцій

• Низьке споживання електроенергії порівняно з багатьма альтернативами

• Збалансовані ресурси без надмірних витрат

• Сильна застаріла екосистема та перевірена надійність

• Гнучка конфігурація за допомогою режимів JTAG або SYSCONFIG

Недоліки

• Нижня стеля продуктивності, ніж FPGA високого класу

• Обмежена логічна щільність та ємність пам'яті

• Ризик застарілості як частина зрілої/припиненої лінії

• Не вистачає розширених функцій, таких як блоки DSP або SERDES

• Компроміси на потужність/ефективність при більш високому використанні

Розміри упаковки LFEC3E-3QN208C

|

Тип |

Параметр |

|

Тип пакету |

208-PQFP (пластиковий квадратний плоска упаковка) |

|

Розмір тіла (l × w) |

28 мм × 28 мм |

|

Висота упаковки (макс) |

3,40 мм |

|

Крок (відстань свинцю) |

0,50 мм |

|

Кількість шпильок |

208 |

|

Довжина свинцю (L) |

0,45 мм ~ 0,75 мм |

|

Ширина свинцю (b) |

0,17 мм ~ 0,27 мм |

|

Загальний проміжок свинцю (D/E) |

30 мм ~ 30,5 мм |

|

Літак для сидіння (A1) |

0,05 мм ~ 0,15 мм |

|

Код пакету |

BFQFP-208 / PQFP-208 |

Виробник LFEC3E-3QN208C

LFEC3E-3QN208C виробляється Корпорація гратів, провідний постачальник малопотужних, малі-форм-факторних програмованих логічних пристроїв.Заснований у 1983 році та штаб-квартира в Хіллсборо, штат Орегон, США, решітки зосереджується на забезпеченні економічно ефективних рішень FPGA та CPLD, пристосованих для комунікацій, обчислювальних, промислових, автомобільних та споживчих додатків.Компанія визнана наголос на архітектурах малої потужності, гнучких стандартів вводу/виводу та рішеннях, що розширюють життєві цикли продукції для вбудованих та промислових ринків.З глобальною присутністю в дизайні, підтримці та розповсюдженні, ґратний напівпровідник продовжує надавати розробникам надійні, ефективні та перепрограмовані платформи, які відповідають поточним, так і застарілим вимогам системи.

Висновок

LFEC3E-3QN208C пропонує практичну комбінацію логічної щільності, вбудованої пам’яті, універсального вводу/виводу та програмуваності в системній системі, що робить її добре підходить для вбудованого управління, комунікацій, прототипування та інструментів.Його підтримка декількох стандартів та гнучких банків напруги забезпечує сумісність як сучасних, так і застарілих систем.Незважаючи на те, що він забезпечує низьке споживання електроенергії, економічну ефективність та надійність, воно має компроміси, такі як обмежена ефективність та потенційна застарілість.Загалом, пристрій залишається надійним вибором для тих, хто шукає збалансованого FPGA для широкого спектру промислових та вбудованих застосувань.

PDF -таблиця

LFEC3E-3QN208C DATASHEETS:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Які інструменти мені потрібні для програмування LFEC3E-3QN208C FPGA?

Ви можете запрограмувати його за допомогою програмного забезпечення для решітки ISPLEVER або Diamond у поєднанні з кабелем JTAG або SYSCONFIG.Ці інструменти підтримують синтез дизайну, моделювання, генерацію Bitstream та програмування в системі.

2. Чи підтримує програму LFEC3E-3QN208C?

Так, його 1,2 В ядра та гнучкі напруги вводу/виводу роблять його хорошим підходящим для систем з низькою потужністю.Він особливо ефективний у конструкціях, що працюють на батареї, або енергоносію, порівняно з багатьма високопродуктивними FPGA.

3. Чи можу я використовувати LFEC3E-3QN208C для пам'яті DDR2 або DDR3?

Ні, цей FPGA офіційно підтримує DDR SDRAM до DDR-400.Для сумісності DDR2/DDR3 рекомендується новіші сім'ї FPGA, оскільки вони включають більш вдосконалені контролери пам'яті.

4. Яка максимальна робоча температура для LFEC3E-3QN208C?

Зазвичай він доступний у комерційних (від 0 ° C до +70 ° C) та промислові (-40 ° C до +85 ° C) температури.Завжди перевіряйте таблицю даних на точний код замовлення частини, щоб забезпечити правильну оцінку.

5. Як LFEC3E-3QN208C порівнюється з FPGA високим класом з точки зору продуктивності?

Він забезпечує надійну продуктивність для програм середнього класу, але не вистачає вдосконалених функцій, таких як SERDE, шматочки DSP або дуже висока логічна щільність.Якщо вам потрібні, вища решітка або конкурент FPGA, як пристрої Xilinx або Intel, краще підходять.

OP400HS Precision Quad OP AMP: Особливості, Покін, додатки та альтернативи

на 2025/10/2

ADV7123JST240 Video DAC: Таблиця, функції, програми та альтернативи

на 2025/09/28

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147765

-

USB-C Pinout та функції

на 2000/04/18 111994

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83753

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79548

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66949

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63094

-

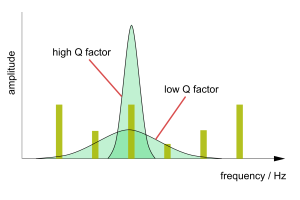

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63028

-

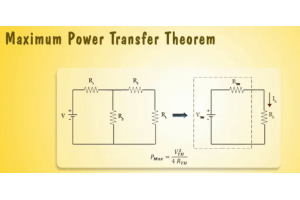

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54094

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52175