EP20K100EFC324-1X FPGA: Особливості, технічні характеристики, програми та посібник з програмування

EP20K100EFC324-1X-це програмований мікросхема (FPGA) із серії Intel Altera Apex-20Ke®.Він призначений для обробки складних цифрових схем та підтримує високошвидкісну обробку даних.Цей посібник пояснює його функції, технічні характеристики, як його програмувати та його переваги, що робить його корисним ресурсом для всіх.Каталог

Огляд EP20K100EFC324-1X

З EP20K100EFC324-1X є частиною серії Altera Apex-20Ke® Intel, польовим програмованим масивом затвора (FPGA), розробленим для програмованих логічних програм високої щільності, які потребують складних інтеграцій System-On-A-програмовано-CHIP (SOPC).Цей пристрій відрізняється його інтеграцією 4160 логічних елементів або комірок та 416 блоків логічного масиву (лабораторії), що полегшує істотну конфігурацію для різних конструкцій цифрових ланцюгів.Він також може похвалитися значною кількістю вбудованої пам’яті, що надає вимогливих вимог до зберігання даних у FPGA.Подальше підвищення універсальності додатків, EP20K100EFC324-1X підтримує 246 вводу/виводу штифтів і пропонує значну кількість воріт приблизно 263 000 еквівалентних воріт, ефективно працюючи між 1,71 В до 1,89 В.Він упаковується в масив толко-кропу з толководною сіткою (FBGA), який допомагає в надійній фізичній інтеграції в електронні збори.

EP20K100EFC324-1X-це ідеальний вибір, коли ви готові розміщувати з нами основні замовлення для своїх проектів або ліній продуктів.

Моделі CAD EP20K100EFC324-1x

EP20K100EFC324-1x символ

EP20K100EFC324-1X Слід

EP20K100EFC324-1X 3D-модель

EP20K100EFC324-1x Особливості

• Висока логічна щільність: FPGA оснащений 4160 логічними елементами (LES) та 416 блоками логічного масиву (лабораторії).Ця висока щільність логічних комірок дозволяє розробити та виконувати складні цифрові схеми та системи в межах однієї мікросхеми, що робить його ідеальним для додатків, що вимагають надійних можливостей логічної обробки.

• Вбудована пам'ять: Пропонуючи 53 248 бітів з бараном, цей FPGA забезпечує значні вбудовані ресурси пам'яті.Ця функція хороша для додатків, які потребують швидкого зберігання та пошуку даних, що дозволяє ефективно обробляти завдання, що інтенсивно.

• Великі можливості вводу/виводу: З 246 вхідними/вихідними шпильками, EP20K100EFC324-1x забезпечує всебічне підключення та варіанти взаємодії.Цей широкий діапазон можливостей вводу/виводу дозволяє йому легко з'єднуватися з безліччю зовнішніх пристроїв та систем, покращуючи його корисність у складних електронних зборах.

• Багатопостійна підтримка: Пристрій підтримує діапазон основної напруги від 1,71 В до 1,89 В та має взаємозв'язок вводу/виводу Multivolt ™.Це дозволяє FPGA сумісним з іншими електронними компонентами, які працюють на різних логічних рівнях, включаючи 1,8 В, 2,5 В, 3,3 В та 5,0 В, забезпечуючи велику гнучкість у дизайні системи.

EP20K100EFC324-1X Блок-схема

З EP20K100EFC324-1X Блок-схема Представляє внутрішню структуру пристрою FPGA (польового програмного масиву затвора), демонструючи різні його функціональні одиниці.Діаграма складається з взаємопов'язаних логічних блоків, елементів пам'яті, управління годинником та елементів вводу/виводу.В основі дизайну Логічні блоки масиву (Лабораторії), які містять Пошукові таблиці (LUTS) та логіка на основі продуктів.Ці елементи дозволяють гнучку реалізацію логіки, що робить FPGA придатним для високошвидкісної логіки управління, станів стану та функцій DSP.З FastTrack взаємозв'язок Забезпечує швидкісний шлях зв'язку між логічними елементами, забезпечуючи ефективну маршрутизацію сигналу по всьому пристрою.З Схема управління годинником , включаючи функцію Clocklock, забезпечує надійну та синхронізовану операцію шляхом стабілізації та розповсюдження сигналів годинника через FPGA.З Вхідні/вихідні елементи (Іос), розташований навколо тканини FPGA, служить інтерфейсами для зовнішнього зв'язку.Ці ioes підтримують кілька стандартних протоколів, таких як PCI, GTL+, SSTL-3і LVDS, що дозволяє FPGA взаємодіяти з різноманітними зовнішніми системами.Ці IOES забезпечують сумісність з різними рівнями напруги та стандартами сигналізації, підвищуючи універсальність FPGA у вбудованих додатках. Вбудовані блоки пам'яті Забезпечте гнучкі рішення для зберігання в межах FPGA.Ці елементи пам'яті можуть функціонувати як Вміст Адреса пам'яті (CAM), Пам'ять випадкового доступу (Оперативна пам’ять), Пам'ять лише для читання (ROM), Перший у першому (FIFO) буфери та інші структури пам'яті.Можливість інтегрувати пам'ять безпосередньо в тканині FPGA покращує ефективність обробки даних, знижуючи зовнішні залежності пам'яті та затримку.

Технічні характеристики EP20K100EFC324-1x

|

Тип |

Параметр |

|

Виробник |

Інтель |

|

Серія |

Apex-20Ke® |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Кількість лабораторій/CLB |

416 |

|

Кількість логічних елементів/клітин |

4160 |

|

Загальні шматочки оперативної пам’яті |

53248 |

|

Кількість вводу/виводу |

246 |

|

Кількість воріт |

263000 |

|

Напруга - постачання |

1,71 В ~ 1,89 В |

|

Монтажний тип |

Поверхневе кріплення |

|

Робоча температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / кейс |

324-BGA |

|

Пакет пристроїв постачальника |

324-FBGA (19x19) |

|

Базовий номер товару |

EP20K100 |

EP20K100EFC324-1x додатки

Мережа та комунікації

Цей FPGA ідеально підходить для мережевого обладнання, таких як маршрутизатори та комутатори, де вона керує маршрутизацією даних, обробкою сигналів та обробкою протоколів.Його висока логічна щільність та великі можливості вводу/виводу дозволяють йому підтримувати складні високошвидкісні операції даних, необхідні в сучасній комунікаційній інфраструктурі.

Системи промислового контролю

У промисловому секторі EP20K100EFC324-1X перевершує в системах автоматизації.Його програмність та надійні можливості обробки дають можливість точного контролю та моніторингу підвищення ефективності експлуатації та надійності у виробничих процесах.

Автомобільна електроніка

FPGA служить компонентом в автомобільних додатках, особливо в розширених системах сприяння драйверам (ADAS) та інвантованих системах транспортних засобів.Він забезпечує необхідну потужність обробки та пристосованість для обробки даних та підтримки складних функціональних можливостей, необхідних у сучасних транспортних засобах.

Побутова електроніка

Завдяки своїй гнучкості та високій продуктивності, EP20K100EFC324-1x також є у споживчій електроніці, як телевізори високої чіткості та ігрові консолі.Він підтримує складні функціональні можливості та СНІД у скороченні циклів розвитку продукції, відповідаючи швидким попитом на ринок побутової електроніки.

Медичні пристрої

У медичній галузі цей FPGA сприяє функціональності медичного обладнання для візуалізації та діагностичних інструментів.Його здатність обробляти дані з високою швидкістю гарантує, що ці пристрої можуть забезпечити точні та своєчасні діагностичні результати для ефективного медикаментозного лікування та візуалізації.

EP20K100EFC324-1x Подібні частини

EP20K100EFC324-1X етапи програмування

Для ефективного програмування EP20K100EFC324-1X, члена серії FPGA Apex-20KE Apex-20Ke®, важливо дотримуватися структурованої послідовності кроків.Цей процес гарантує, що ваша конструкція ефективно переводиться у формат, який може виконувати FPGA.Нижче я окреслюю детальний підхід до програмування цієї моделі FPGA, інтегруючи кроки та модифікації, характерні для цього пристрою.

1. Вхід дизайну

Почніть з створення вашого цифрового дизайну.Використовуйте апаратні мови (HDL), такі як VHDL або Verilog, які дозволяють описати функціональність обладнання та логіку вашої системи.Такі інструменти, як Quartus II Altera, пропонують всебічне середовище для написання, тестування та складання вашого коду на ЛПВЩ.Переконайтесь, що ваш дизайн модульний, що полегшує налагодження та масштаб.

2. Синтез

Після завершення вашого дизайну, наступним кроком є синтез, де код HDL переводиться в мережу.Цей Netlist представляє взаємопов'язаний список воріт, шльопанок та інших апаратних елементів, що складають ваш дизайн.Під час синтезу код оптимізований для специфічної архітектури EP20K100EFC324-1x, гарантуючи, що дизайн ефективно використовує ресурси FPGA.Для цієї мети можна використовувати такі інструменти, як Synplify Pro або інструмент синтезу в кварталі II.Важливо зосередитись на оптимізації дизайну для задоволення термінів та обмежень ресурсів.

3. Реалізація

Після синтезу відбувається реалізація.Цей крок передбачає відображення мережі до фактичного обладнання FPGA.Він включає розміщення логічних елементів всередині FPGA та маршрутизацію з'єднань між ними.Програмне забезпечення Quartus II сприяє цьому процесу за допомогою його інструментів впровадження, які керують розміщенням та маршрутизацією для задоволення бажаних годин тактової швидкості та показників продуктивності.Під час впровадження вам може знадобитися ітерувати на своєму дизайні на основі зворотного зв'язку з інструментів аналізу часу, щоб переконатися, що всі вимоги до ефективності виконуються.

.

Після успішної реалізації наступний етап генерує Bitstream.Це двійковий файл, який буде завантажений на FPGA.Bitstream містить налаштовані дані для кожного програмованого елемента у FPGA, налаштовуючи пристрій для виконання функцій відповідно до вашої конструкції.Програмне забезпечення Quartus II може генерувати цей Bitstream, який потім готовий до завантаження в FPGA.

5. Програмування FPGA

Останнім кроком є програмування FPGA з генерованим бітом.Це можна зробити за допомогою апаратного програміста, сумісного з EP20K100EFC324-1x, наприклад USB-Blaster.Підключіть програміст до своєї плати розробки, де встановлено FPGA, і використовуйте інструмент програміста Quartus II для перенесення Bitstream в FPGA.Цей крок завантажить вашу конструкцію на FPGA, і він почне працювати відповідно до логіки, визначеної у вашому коді HDL.

EP20K100EFC324-1X Переваги

Висока інтеграція

EP20K100EFC324-1x пропонує високі можливості інтеграції завдяки великій кількості логічних елементів та вбудованій пам'яті.Ця інтеграція дозволяє консолідувати кілька функціональних можливостей в один пристрій.Як результат, системи можна спростити, зменшуючи загальний кількість компонентів, необхідний фізичний простір та потенційні точки відмови в електронних конструкціях.

Гнучка реалізація логіки

Архітектура EP20K100EFC324-1X підтримує як таблицю пошуку (LUT), так і на основі продукту на основі логіки.Ця гнучкість у реалізації логіки дозволяє оптимізувати FPGA для широкого спектру додатків, від простих логічних воріт до складних комбінаційних схем.Він забезпечує перевагу з точки зору універсальності дизайну і може вмістити широкий спектр цифрових функціональних можливостей.

Розширена структура взаємозв'язку

Завдяки ієрархічній структурі взаємозв'язку, FPGA включає взаємозв'язок Local, Megalab ™ та FastTrack®.Ці спеціалізовані ресурси маршрутизації підвищують ефективність маршрутизації сигналу та покращують загальну продуктивність пристрою.Ця вдосконалена структура взаємозв'язку корисна для конструкцій, які потребують високошвидкісної передачі даних та низької затримки, що робить FPGA ідеальним для високоефективних обчислень та телекомунікацій.

Управління годинником

EP20K100EFC324-1X включає технологію Clocklock та Clockboost, яка допомагає в ефективному управлінні годинником.Ці функції допомагають підтримувати цілісність сигналу годинника протягом усього FPGA, зменшуючи тремтіння та підвищення надійності сигналу.Ефективне управління годинником необхідне для синхронних цифрових схем, забезпечуючи стабільну та передбачувану роботу в різних умовах навколишнього середовища.

Гнучкість дизайну

Програмований характер EP20K100EFC324-1X дозволяє налаштувати обладнання до конкретних потреб та переналаштувати FPGA для різних додатків або оновлень.Ця гнучкість означає, що один FPGA може використовуватися в різних проектах, що сприятливо в динамічному технологічному ландшафті, де вимоги можуть швидко змінюватися.

Швидке прототипування

FPGA, як EP20K100EFC324-1x, дозволяють швидко прототипувати цифрові схеми.Ви можете швидко розвивати та повторювати конструкції без тривалого часу, пов'язаного з розробкою ASIC.Ця здатність швидко моделювати та тестувати нові конструкції прискорює процес розробки, що призводить до більш швидких інновацій та скорочення часу на ринок.

Ефективність витрат

Інтеграція декількох функцій в межах однієї FPGA зменшує потребу в додаткових дискретних компонентах, що може призвести до економії витрат як в закупівлі, так і в складі.Ця інтеграція також спрощує виробничий процес і може зменшити загальну складність системи, що призводить до зниження витрат на обслуговування та модернізації над життєвим циклом продукту.

Довгострокова підтримка

Реконфігурований аспект EP20K100EFC324-1X забезпечує оновлення обладнання для виправлення помилок, покращення продуктивності або додавання нових функцій, не вимагаючи фізичних змін обладнання.Ця довгострокова підтримка та пристосованість захищають інвестиції та дають можливість пристроям залишатися актуальними, коли з'являються нові стандарти та технології.

EP20K100EFC324-1X Розміри упаковки

EP20K100EFC324-1x-FPGA від серії Altera Apex-20Ke®, що розміщується в 324-м'яч з тонкою кашкою сітки (FBGA) пакет.Його розміри упаковки такі:

• Стовп: 1 мм

• Довжина × ширина: 19 мм × 19 мм

• Область: 361 мг²

EP20K100EFC324-1X Виробник

EP20K100EFC324-1X-це модель із серії Apex-20Ke® полів програмованих масивів затвора (FPGA), спочатку розроблених Altera.Після придбання Intel Altera у 2015 році ця FPGA та інші продукти Altera стали частиною широкого портфеля програмованих рішень Intel.Як результат, Інтель продовжує підтримувати лінійки продуктів Altera, одночасно інтегруючи їх із власними вдосконаленими технологічними пропозиціями.Незважаючи на те, що EP20K100EFC324-1x був класифікований як застарілий і більше не виробляється, його спадщина підтримується в Intel, що рекомендує нові моделі FPGA для поточних додатків для забезпечення довгострокової підтримки та доступності.

Висновок

EP20K100EFC324-1X-це потужний і гнучкий FPGA, який дозволяє створювати та перевіряти спеціальні цифрові схеми.Він пропонує високопродуктивну, вбудовану пам'ять та підтримку багатопостевої, що робить її корисною у багатьох галузях.Цей посібник провів вас через основні функції, дизайн та кроки, щоб програмувати цей FPGA просто, щоб ви могли легко зрозуміти та використовувати його.

PDF -таблиця

EP20K100EFC324-1X ДАТЕЛИ:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Як EP20K100EFC324-1X порівнюється з новішими моделями FPGA?

EP20K100EFC324-1X залишається потужним FPGA для застарілих систем та промислових додатків, які потребують високої логічної щільності та гнучких можливостей вводу/виводу.Однак, порівняно з сучасними FPGA, такими як серія циклону, ARRIA або Stratix Intel, йому не вистачає підвищеної енергоефективності, високошвидкісних приймачів та прискорення AI.Якщо ви розробляєте нову систему, ми можемо запропонувати еквівалентні або модернізовані моделі.

2. Чи підтримує EP20K100EFC324-1x зовнішні інтерфейси пам'яті, такі як DDR або SRAM?

Так, EP20K100EFC324-1X підтримує зовнішні інтерфейси пам'яті, включаючи SRAM та SDRAM.Однак він не підтримує DDR2/DDR3.Якщо необхідно знадобитися взаємозв'язок пам'яті, додаткова зовнішня логіка або новіша FPGA може знадобитися.

3. Чи можу я перенастролювати EP20K100EFC324-1x кілька разів?

Так, як і всі FPGA, цей пристрій повністю перепрограмований.Однак, якщо ви використовуєте нестабільну конфігурацію, вам знадобиться зовнішня пам'ять (наприклад, послідовний пропуск), щоб зберегти конструкцію після силового циклу.

4. Чи можу я програмувати EP20K100EFC324-1x за допомогою програмного забезпечення Intel Quartus?

Так, ви можете запрограмувати EP20K100EFC324-1X за допомогою Intel Quartus II (Legacy Versions), оскільки ця FPGA належить до сім'ї Apex-20Ke®.Переконайтесь, що ваша версія Quartus II підтримує цей пристрій, оскільки новіші випуски кварталу Prime не підтримують застарілі FPGA.

5. Які вимоги до живлення я повинен враховувати при використанні EP20K100EFC324-1x?

EP20K100EFC324-1x працює з діапазоном основної напруги від 1,71 В до 1,89 В.Він також має технологію введення/виводу Multivolt ™, що підтримує рівні логіки 1,8 В, 2,5 В, 3,3 В та 5,0 В.Переконайтесь, що ваше джерело живлення відповідає цим вимогам напруги для стабільних показників.

XCV200-6FG456C FPGA: Особливості, технічні характеристики, програмування та додатки

на 2025/03/20

Чому компоненти 0603 популярні в сучасній електроніці

на 2025/03/20

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147770

-

USB-C Pinout та функції

на 2000/04/18 112006

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

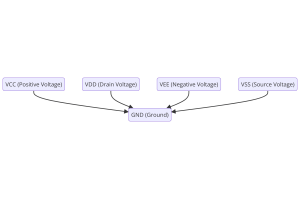

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83768

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79562

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66958

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63098

-

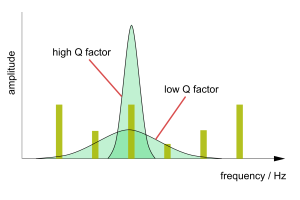

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63040

-

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54095

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52182