XCV200-6FG456C FPGA: Особливості, технічні характеристики, програмування та додатки

XCV200-6FG456C-це потужний FPGA (польовий запрограмований масив воріт) з серії AMD Xilinx Virtex®.Цей посібник пояснює його функції, макет PIN -коду, кроки програмування та використання.Завдяки високій потужності обробки, гнучким параметрам проектування та сильними можливостями введення/виходу (вводу/виводу), ця FPGA допомагає створювати швидкі та надійні цифрові системи.Незалежно від того, чи працюєте ви над мережевими системами, системами управління чи користувальницькою електронікою, цей посібник допоможе вам зрозуміти, як XCV200-6FG456C може використовуватися у ваших проектах.Каталог

Огляд XCV200-6FG456C

З XCV200-6FG456C є помітною моделлю в сімействі AMD Xilinx Virtex® FPGA, розроблена для забезпечення надійних програмованих логічних рішень для складних цифрових систем.Цей специфічний мікросхема охоплює приблизно 236 666 системних воріт і має 1176 налаштованих логічних блоків (CLB) та 5 292 логічних комірок.Він також включає 57 344 загальних бітів оперативної пам’яті та підтримує 284 штифти вводу/виводу, розміщені в пакеті масиву з тонкою точкою сітки з тонкою точкою (FBGA), розміром 23 мм х 23 мм.Ця модель працює на номінальній напрузі 2,5 В, діапазон від 2,375 В до 2,625 В і може функціонувати в межах температурного діапазону від 0 ° С до 85 ° С.Більш широка серія Virtex® обслуговує цілий ряд застосувань з щільністю від 50 000 до понад 1 мільйона воріт системних та системних годинних таблиць до 200 МГц.Він підтримує численні стандарти вводу/виводу, включаючи LVTTL, LVCMOS та PCI, серед інших.Такі функції, як петлі з затримкою (DLL), налаштовані логічні блоки з вбудованою пам'яттю та спеціалізована логіка для арифметичних операцій, покращують його функціональність.Виготовлений за допомогою 5-шарового металевого процесу 0,22 мкм, сім'я Virtex® гарантує продуктивність та надійність.

Якщо ви хочете інтегрувати технологію FPGA вищого рівня у свою продукцію чи системи, купувати XCV200-6FG456C оптом з нами-це розумний хід.Він відповідає галузевим стандартам і тримає вас перед майбутніми потребами технологій.

Особливості XCV200-6FG456C

• Ворота системи: XCV200-6FG456C пропонує приблизно 236 666 системних воріт.Цей високий кількість воріт дозволяє здійснювати складні інтегровані цифрові логічні схеми на одному мікросхемі, що підвищує як продуктивність, так і універсальність у ряді додатків.

• Логічні ресурси: Він включає 1176 налаштованих логічних блоків (CLB) та 5292 логічних комірок.Ці ресурси корисні для розробки гнучких та масштабованих цифрових схем.CLB можна запрограмувати для виконання найрізноманітніших логічних функцій, тоді як велика кількість логічних комірок дозволяє обробляти широкі логічні операції та процеси.

• Пам'ять: Пристрій забезпечує 57 344 біт оперативної пам’яті, розподілених між його логічними блоками.Ця вбудована оперативна пам’ять використовується для додатків, які потребують швидкого та ефективного зберігання даних та пошуку, підтримуючи високошвидкісні операції даних, інтеграл для сучасних цифрових систем.

• Можливості вводу/виводу: З 284 вхідними/вихідними штифтами, XCV200-6FG456C полегшує широкі можливості взаємодії.Ці шпильки вводу/виводу підтримують різні стандарти сигналу і дозволяють FPGA ефективно спілкуватися з іншими компонентами в системі, такими як пристрої пам'яті, процесори та периферійні пристрої.

• Діапазон напруги та температури: Працюючи при номінальній напрузі 2,5 В, з прийнятним діапазоном від 2,375 В до 2,625 В, цей FPGA розроблений для споживання низької потужності, зберігаючи надійну продуктивність.Він може працювати в межах температурного діапазону від 0 ° С до 85 ° С, забезпечуючи надійність в різних умовах навколишнього середовища.

XCV200-6FG456C Функція PIN-коду

З XCV200-6FG456C Функція PIN-коду є структурованим представленням призначень PIN -коду FPGA, класифікованих у різні банки (Банк 0 до банку 7.).Кожен банк групує шпильки на основі їх функції та фізичного розміщення на пакеті FPGA.Система нумерації та маркування відповідає сітковому малюнку, де рядки позначаються літерами (A, B, C тощо), а стовпці за числами (1, 2, 3 тощо), що полегшує швидку ідентифікацію конкретних штифтів.Ці банки відповідають різним функціям вводу/виводу, потужності, землі та спеціальній маршрутизації сигналу.Штифти присвоюються різні функціональні угруповання, включаючи вводу/виводу загального призначення (GPIO), які часто позначені як "G" (загальний вхід/вихід), "V" (живлення напруги) та "O" (вихід).Потужність і наземні штифти позначені чітко, забезпечуючи стабільну роботу FPGA.Шпильки спеціального призначення, такі як входи годин, скидання та контрольні сигнали, ідентифікуються з такими символами, як "R" або "T."Деякі шпильки також виконують спеціальні ролі комунікації, включаючи конфігурацію JTAG та високошвидкісне залучення, для програмування та налагодження.

XCV200-6FG456C Блок-схема

Блок введення/виводу

Діаграма представляє Блок введення/виводу (IOB) Структура XCV200-6FG456C FPGA, яка є членом сімейства Xilinx Virtex.Діаграма демонструє ключові елементи, що беруть участь у вхідних та вихідних операціях, підкреслюючи механізми потоку даних та управління.На основі діаграми для реєстрації сигналів, виводу та тридержавного контролю використовуються три D-флопи.Вихідний регістр керується сигналом OCE (включення вихідного годинника), який визначає, коли вихідні дані зафіксовані.Аналогічно, тридержавний регістр контролюється TCE (Tri-State Clock Увімкнено), що дозволяє або відключає вихідний буфер.Регістр введення фіксує вхідні дані та застосовує програмовану затримку, перш ніж передавати її до внутрішньої логіки FPGA через IBUF (вхідний буфер).OBUFT (тридержавний буфер виходу) гарантує, що FPGA може або керувати сигналом на колодку (штифт вводу/виводу), або розмістити його у стані високого імпедансу, залежно від логіки управління.На майданчику входить слабкий ланцюг зберігачів для підтримки останнього відомого логічного стану, коли жодного активного драйвера не є, запобігаючи непередбачуваним плаваючим умовам.Референтна напруга (VREF) використовується для певних стандартів введення, таких як SSTL або HSTL, які потребують точних рівнів напруги для належної роботи.Загалом, ця структура IOB дозволяє FPGA керувати високошвидкісними передачами даних, підтримувати різні стандарти вводу/виводу та забезпечувати гнучкий контроль над термінами та цілісністю сигналу.

Серійний режим Master/Slave

З Серійний режим Master/Slave Блок-схема ілюструє процес конфігурації FPGA VIRTEX, зокрема XCV200-6FG456C, коли запрограмовано в конфігурації ланцюга ромашки за допомогою послідовного EEPROM (XC1701L).У цій установці один пристрій Virtex працює як майстер, керуючи годинником конфігурації (CCLK) та серійно передаваючи дані конфігурації в додаткові підлеглі FPGA в ланцюзі.Основна FPGA ініціює процес конфігурації, стверджуючи сигнал програми, скинувши всі пристрої в ланцюзі.Після того, як ініціалізація буде завершена, сигнал INIT вказує на готовність, а дані конфігурації протікають із послідовного EEPROM (XC1701L) до DIN (Data In) PIN -коду головного FPGA.Master FPGA зчитує дані з EEPROM та пересилає їх через Dout (дані) до наступних підлеглих FPGA, синхронізуючи передачу даних за допомогою сигналу CCLK.Зроблений сигнал використовується для позначення успішної конфігурації, з необов'язковим резистором, що забезпечує стабільний високий стан, коли конфігурація завершена.XC1701L EEPROM контролюється головним FPGA за допомогою CLK, даних, CE (Chip Enable) та Скидання/OE (Вихід Увімкнено), гарантуючи, що дані про збережену конфігурацію будуть правильно отримані.Цей метод конфігурації є ефективним для програмування декількох FPGA за допомогою одного EEPROM, зменшення складності зовнішньої проводки та забезпечення всіх пристроїв отримують синхронізовані дані конфігурації.

Специфікація XCV200-6FG456C

|

Тип |

Параметр |

|

Виробник |

AMD XILINX

|

|

Серія |

Virtex® |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Кількість лабораторій/CLB |

1176 |

|

Кількість логічних елементів/клітин |

5292 |

|

Загальні шматочки оперативної пам’яті |

57344 |

|

Кількість вводу/виводу |

284 |

|

Кількість воріт |

236666 |

|

Напруга - постачання |

2.375V ~ 2.625V |

|

Монтажний тип |

Поверхневе кріплення |

|

Робоча температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / кейс |

456-BBGA |

|

Пакет пристроїв постачальника |

456-FBGA (23x23) |

|

Базовий номер товару |

XCV200 |

Xcv200-6fg456c додатки

Телекомунікації та мережа

XCV200-6FG456C перевершує телекомунікаційні та мережеві програми завдяки здатності обробляти високошвидкісні передачі даних та складні завдання обробки сигналів.Її висока кількість воріт та надійні можливості вводу/виводу дозволяють йому підтримувати такі функції, як обробка пакетів, модуляція/демодуляція сигналу та протоколи виправлення помилок.

Цифрова обробка сигналів (DSP)

Ідеально підходить для додатків DSP, ця FPGA може виконувати швидкі та складні математичні обчислення, необхідні в технологіях аудіо та відео обробки.Будь то для мультимедійних систем, розпізнавання голосу чи потокових служб, потужних можливостей обробки XCV200-6FG456C та вбудованої підтримки пам'яті ефективної та високоякісної обробки сигналів.

Системи промислового контролю

У промисловій автоматизації XCV200-6FG456C забезпечує необхідну продуктивність для управління системами управління та автоматизаційними мережами.Його здатність виконувати кілька завдань управління одночасно, забезпечуючи час реагування, робить його придатним для програм у контролі процесу, робототехніки та машинному зорі.

Медичні інструменти

Точність та швидкість FPGA чудово підходять для медичного обладнання для візуалізації та діагностики, де це допомагає в обробці складних алгоритмів для зображень, таких як МРТ, ультразвук та КТ.Можливості XCV200-6FG456C гарантують, що він може обробляти високу пропускну здатність даних та складну обробку, необхідну в сучасних медичних технологіях.

Xcv200-6fg456c подібні частини

Xcv200-6fg456c кроки програмування

Етапи програмування для XCV200-6FG456C:

1. Вхід дизайну

Початкова фаза програмування FPGA передбачає визначення цифрової логіки та функціональності вашої системи.Це можна зробити за допомогою мови описів апаратних засобів (HDL), таких як VHDL або Verilog, де ви пишете код, який визначає, як FPGA обробляє дані та взаємодіє з іншим обладнанням.Схематичні інструменти введення, доступні в програмному забезпеченні FPGA, таких як Xilinx ISE або Vivado, можуть бути використані.Цей метод передбачає створення візуального представлення логіки шляхом перетягування та відкидання компонентів, які деякі вважають більш інтуїтивно зрозумілими, ніж код написання.

2. Синтез

Після завершення дизайну наступним кроком є синтез, де такий інструмент, як XST XST (технологія синтезу Xilinx) перетворює ваш код на ЛПВЩ або схематичну конструкцію в мережу.Цей Netlist описує схему з точки зору загальних цифрових компонентів, таких як логічні ворота та регістри.Процес синтезу також передбачає оптимізацію дизайну для задоволення вимог до продуктивності та мінімізації використання ресурсів для ефективної роботи FPGA.

3. Реалізація

Процес впровадження починається з перекладу, поєднуючи вашу конструкцію з файлами обмежень, які визначають параметри, такі як частоти годин та призначення PIN -коду.Після перекладу етап картографування призначає елементи вашого мережі конкретним фізичним ресурсам на FPGA, як-от таблиці пошуку (LUTS) та шльопанці.Потім фаза розміщення та маршрутизації визначає фізичні місця кожного компонента в архітектурі FPGA та встановлює з'єднання між ними через програмовані ресурси взаємозв'язку.Цей етап чудово підходить для досягнення бажаних показників ефективності, включаючи частоти годин.

.

Після успішного розміщення та маршрутизації інструмент генерує Bitstream, двійковий файл конфігурації, який містить всю інформацію про програмування для FPGA.Часто рекомендується імітувати остаточний дизайн після розміщення, щоб переконатися, що Bitstream буде вести себе, як очікувалося в умовах.Цей етап перевірки допомагає уникнути потенційних проблем під час фактичної роботи.

5. Конфігурація

Заключний крок передбачає завантаження Bitstream у FPGA за допомогою різних методів конфігурації.Режим Slave-Serial, простий та економічно ефективний варіант, налаштовує FPGA через зовнішній головний пристрій, який надсилає дані серійно.У режимі Master-Serial FPGA автономно читає Bitstream з прикріпленого серійного пропусту.Для високошвидкісних конфігурацій режим SelectMap дозволяє зовнішньому мікропроцесору швидко завантажувати дані в FPGA.Крім того, режим JTAG використовується не тільки для програмування, але і для тестування та налагодження, використовуючи стандартний інтерфейс для програмування в системі та тестування граничних сканів.

Xcv200-6fg456c переваги

Виконання

Серія xilinx virtex, до якої належить XCV200-6FG456C, оптимізований для високошвидкісних показників, пропонуючи системні годинникові швидкості до 200 МГц.Це робить його добре підходить для додатків, які потребують швидкої обробки даних, забезпечення ефективного поводження з складними алгоритмами та високошвидкісними операціями, такими як телекомунікації, обробка та мультимедіа.

Підтримка стандартів вводу/виводу

Цей FPGA підтримує широкий діапазон стандартів введення/виводу, включаючи LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT та AGP.Такі обширні стандарти вводу/виводу дозволяють безперешкодно інтегруватися XCV200-6FG456C для безперешкодного інтеграції з різними системними компонентами, покращуючи його корисність у різних цифрових екосистемах.Ця гнучкість дозволяє адаптувати FPGA до різних умов взаємодії без модифікацій системи.

Управління годинником

XCV200-6FG456C включає в себе кілька петлей із затримкою (DLL) для розподілу годин та управління в системі.Ці DLL допомагають вдосконалити системні терміни та надійність, надаючи точні годинникові сигнали, необхідні для синхронних операцій.Ця особливість важлива для зменшення помилок системи та підвищення загальної продуктивності, особливо у складних конструкціях, що потребують точних термінів та синхронізації.

Гнучкість дизайну

Завдяки 1176 налаштованих логічних блоках та 5292 логічних комірок, XCV200-6FG456C пропонує значні логічні ресурси з можливістю впровадити різноманітний спектр функціональних можливостей.Від простої логіки клею до заплутаних цифрових систем цей FPGA підтримує складні вимоги до проектування, що робить її ідеальною для додатків у спеціальних обчисленнях, цифровій обробці сигналів та прототипування.

Швидке прототипування

FPGA, як XCV200-6FG456C, відомі своєю здатністю підтримувати швидке прототипування.Цей пристрій дозволяє швидко ітерації проектування і його можна перенастроювати в полі, що є перевагою для циклів розвитку, оскільки він скорочує час на ринок.Він також ефективно адаптується до зміни вимог або оновлень у специфікаціях проекту, гарантуючи, що остаточні продукти в курсі останніх технологічних стандартів.

Інтеграційна здатність

Інтеграційні можливості XCV200-6FG456C полегшують консолідацію декількох дискретних компонентів в один мікросхему.Ця інтеграція може призвести до зниження складності системи, зниження енергоспоживання та економії витрат.Мінімізуючи кількість необхідних окремих компонентів, цей FPGA спрощує процеси проектування та покращує надійність та компактність загальної системи.

Розміри упаковки XCV200-6FG456C

XCV200-6FG456C-це поле програмований масив воріт (FPGA) із серії Virtex® AMD, розміщеного в упаковці з толководною сіткою з толководною кулею (FBGA).

• Тип пакету: 456-FBGA

• Розмір пакету: 23 мм х 23 мм

• Куля: 1,0 мм

XCV200-6FG456C Виробник

XCV200-6FG456C-це поле програмований масив воріт (FPGA), спочатку розроблений Xilinx, компанією, відомою своїми високоефективними програмованими логічними пристроями.Після придбання Xilinx за допомогою AMD, XCV200-6FG456C тепер асоціюється з AMD як його нинішнього виробника.Однак ця модель FPGA застаріла і вже не у виробництві.AMD продовжує підтримувати новіші архітектури FPGA з підвищеною продуктивністю, енергоефективністю та розширеною довголіттям, що робить сучасні альтернативи кращими для нових конструкцій.

Висновок

XCV200-6FG456C-це універсальний і високошвидкісний FPGA, корисний для багатьох технологічних додатків.Хоча це вже не робиться, це все ще є хорошим вибором для старих систем, які потребують надійної продуктивності.Цей посібник висвітлював свою конструкцію, кроки програмування та практичне використання, полегшило розуміння, як він працює та як його можна використовувати.По мірі того, як нові FPGA стають доступними, ви можете використовувати ці знання для вибору правильної FPGA для ваших потреб та вдосконалення цифрових конструкцій.

PDF -таблиця

XCV200-6FG456C DATASHEETS:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Яке споживання електроенергії XCV200-6FG456C?

XCV200-6FG456C працює при 2,5 В, з діапазоном напруги від 2,375 В до 2,625 В.Споживання електроенергії залежить від використання логіки та тактової частоти, але як старший FPGA, воно може бути менш ефективним, ніж новіші пристрої Xilinx.Слід враховувати належне управління енергією та розсіювання тепла.

2. Як XCV200-6FG456C порівнюється з XCV200-6FG256C?

XCV200-6FG456C має більший пакет (FBGA 456 BALL) порівняно з XCV200-6FG256C (256-куля FBGA), пропонуючи більше штифтів вводу/виводу (284 проти 172) та потенційно кращих показників для додатків, що потребують великого втручання.Якщо ваш дизайн покладається на більше можливостей вводу/виводу, XCV200-6FG456C-кращий вибір.

3. Чи можу я перепрограмувати XCV200-6FG456C кілька разів?

Так, XCV200-6FG456C-це FPGA на основі SRAM, тобто його можна перепрограмувати необмежену кількість разів, поки потужність надається.Однак вам знадобиться зовнішня неповнолітня пам'ять (EEPROM або FLASH), щоб зберегти Bitstream після циклу живлення.

4. Чи підтримує високошвидкісну серійну комунікацію XCV200-6FG456C?

XCV200-6FG456C підтримує декілька стандартів вводу/виводу, таких як LVTTL, LVCMOS, PCI, GTL, HSTL та SSTL, але він не має вбудованих високошвидкісних Serdes (селіалізатор/десеріалайзер) або транзійців, таких як сучасні FPGA.Для додатків, що потребують швидкісних серійних посилань (наприклад, PCIE, Gigabit Ethernet або HDMI), розглянемо новіші моделі FPGA.

5. Як XCV200-6FG456C порівнюється з новішими моделями FPGA?

XCV200-6FG456C належить до старшого покоління FPGA.Порівняно з сучасними FPGA Virtex, він має нижчу кількість воріт, повільніші швидкості тактової швидкості та обмежену ефективність потужності.Нові моделі пропонують більш високу логічну щільність, більш вбудовану пам'ять, вдосконалені блоки DSP та менший споживання електроенергії, що покращує їх для сучасних додатків.

AD73322AR PINOUT, функції та технічні деталі пояснюються

на 2025/03/21

EP20K100EFC324-1X FPGA: Особливості, технічні характеристики, програми та посібник з програмування

на 2025/03/20

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147778

-

USB-C Pinout та функції

на 2000/04/18 112033

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111352

-

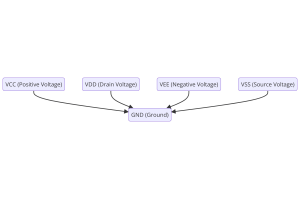

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83792

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79602

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66976

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63111

-

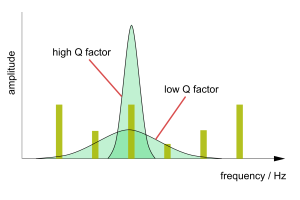

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63044

-

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54097

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52198