EP2S60F672C4 FPGA: Особливості, програми, Посібник з програмування та даних

У цьому посібнику ви отримаєте чіткий огляд EP2S60F672C4, потужної FPGA від родини Intel's Stratix II.Ви дізнаєтесь про його основні особливості, архітектуру, структуру блоку та технічні характеристики, щоб зрозуміти, як вона вписується в розширені цифрові конструкції.Він також проводить вас через свої кроки, програми, переваги та недоліки, щоб ви могли точно побачити, де і як можна використовувати цей пристрій.Каталог

Що таке EP2S60F672C4?

З EP2S60F672C4 -FPGA високої щільності від Intel (раніше Altera), що належить родині Stratix II.Побудований на процесі 90 нм, 1,2 V мідний SRAM, він забезпечує значну логічну ємність у пакеті FBGA на 672 кулі, що робить його ідеальним для складних цифрових систем.У рамках серії EP2S, пристрій "60" сидить у середині до верхнього діапазону лінійки Stratix II, пропонуючи сильний баланс логічної щільності, вбудованої пам'яті та ресурсів вводу/виводу.Відомий своєю надійною архітектурою та надійністю, цей FPGA залишається надійним вибором у багатьох вдосконалених конструкціях.

Шукаєте EP2S60F672C4?Зверніться до нас, щоб перевірити поточні акції, час виконання та ціни.

Моделі CAD EP2S60F672C4

EP2S60F672C4 Символ

EP2S60F672C4 Слід

3D -модель EP2S60F672C4

EP2S60F672C4 Особливості

• Розширений процес 90 нм, 1,2 В CMOS

EP2S60F672C4 виготовляється на процесі мідних CMOS 90 нм, який працює при 1,2 В ядрі напруги.Ця технологія забезпечує високу швидкість, зменшення споживання електроенергії та більшу логічну щільність порівняно зі старими поколіннями FPGA.

• Архітектура адаптивного логічного модуля (ALM)

Пристрій використовує милостиню як свій логічний будівельний блок замість традиційних логічних елементів.Ця архітектура покращує використання ресурсів, що дозволяє ефективніше реалізувати більш складні логічні функції в межах однієї і тієї ж кремнієвої області.

• Висока логічна щільність

Приблизно 60 440 логічних елементів (24 176 милостині), FPGA підтримує великі та складні цифрові конструкції.Ця висока ємність робить її придатною для таких додатків, як обробка сигналів, комунікації та вбудовані системи управління.

• Trimatrix ™ на мікросхемі

EP2S60F672C4 інтегрує три типи оперативних блоків (M512, M4K та M-RAM), щоб забезпечити загальну суму близько 2,4 млн. Мбіт вбудованої пам'яті.Ця суміш дозволяє ефективно впроваджувати невеликі FIFO, середні буфери та великі спогади з подвійним портом.

• Виділені блоки DSP

Пристрій включає 36 виділених блоків DSP, призначених для арифметичних операцій, таких як мультиплікації, накопичення та фільтрація ялинок.Ці блоки підвищують продуктивність у обчислювальній кількості завдань, зберігаючи загальні логічні ресурси.

• Високошвидкісна цілісність вводу/виводу та сигналу

Він підтримує різні стандарти вводу/виводу в один раз, а також схема динамічного фазового вирівнювання (DPA).Ці функції дозволяють стабільну швидкісну передачу даних до 1 Гбіт / с, забезпечуючи надійне спілкування із зовнішніми компонентами.

• Багата зовнішня підтримка інтерфейсу пам'яті

FPGA сумісна з DDR, DDR2, QDR II, RLDRAM II та іншими стандартами пам'яті.Вбудована підтримка інтерфейсу спрощує дизайн плати та досягає високої пропускної здатності даних для інтенсивних додатків для пам'яті.

• Гнучке управління годинником

До 12 PLL на мікросхемі дозволяють множити годинника, поділ, зміщення фаз та перемикання без глюка.Ви можете тонко налаштувати годинникові домени та зменшити тремтіння, підтримуючи внутрішні частоти годин до 500–550 МГц.

• БІТТРЕМНЕ ШВИДКА ТА ПРОПОЗИЦІЯ

EP2S60F672C4 підтримує шифрування Bitstream на основі AES для забезпечення інтелектуальної власності.Він також пропонує можливість віддаленої реконфігурації, що дозволяє в оновленнях поля без заміни пристрою.

Блок -схема Stratix II

Блок -схема Stratix II, як показано для EP2S60F672C4, ілюструє внутрішнє розташування ресурсів логіки, пам'яті та DSP, що утворюють ядро FPGA.Логічні блоки масиву (лабораторії) розташовані в звичайній сітці, оточеній вбудованими оперативними та DSP стовпцями, які забезпечують швидкі арифметичні та мікросхеми зберігання.Периферійні елементи вводу/виводу та тактові мережі кадрують цю структуру, що дозволяє ефективно передати дані та контроль часу між FPGA та зовнішніми пристроями.Ця діаграма є важливою, оскільки вона допомагає зрозуміти, як фізично організовуються різні функціональні блоки, що дозволяє їм оптимізувати розміщення, маршрутизацію та загальну продуктивність системи.

Діаграма Banks Stratix II/O

Ця схема вводу/виводу Stratix II/виводу ілюструє, як групуються вхідні/вихідні штифти EP2S60F672C4 та які електричні стандарти підтримують кожну групу.Кожен банк вводу/виводу призначений для обробки конкретних рівнів напруги, типів сигналізації та таких функцій, як LVTTL, SSTL, LVDS або годинникові вхідні стандарти.Макет показує, як різні банки (наприклад, 1, 2, 5, 6 проти 3, 4, 7, 8 тощо) оптимізовані для диференціальної сигналізації вводу/виводу загального призначення, або для високошвидкісної диференціальної сигналізації, включаючи підтримку входів LVDS/LVPECL на краях.Розуміння цієї структури є важливим при призначенні штифтів, оскільки належний вибір банку забезпечує електричну сумісність, спрощує маршрутизацію плати та максимально збільшує продуктивність FPGA у високошвидкісних конструкціях.

Технічні характеристики EP2S60F672C4

|

Тип |

Параметр |

|

Виробник |

Altera/Intel |

|

Серія |

Stratix® II |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Кількість лабораторій/CLB |

3022 |

|

Кількість логічних елементів/клітин |

60 440 |

|

Загальні шматочки оперативної пам’яті |

2,544,192 |

|

Кількість вводу/виводу |

492 |

|

Напруга - постачання |

1,15 V ~ 1,25 V |

|

Монтажний тип |

Поверхневе кріплення |

|

Робоча температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / кейс |

672-BBGA |

|

Пакет пристроїв постачальника |

672-FBGA (27 × 27) |

|

Базовий номер товару |

EP2S60 |

Програми EP2S60F672C4

1. Цифрова обробка сигналів (DSP) та фільтрація

EP2S60F672C4 добре підходить для реалізації високоефективних функцій DSP, таких як FIR та IIR, обробка FFT та складні арифметичні операції.Його спеціальні блоки DSP ефективно обробляють мультиплікації та скупчення, звільняючи загальні логічні ресурси для інших завдань.Пам'ять на Chip Trimatrix ™ дозволяє плавно буферизацію даних та трубопроводку, що чудово підходить для обробки в режимі реального часу при високих швидкостях вибірки.Це робить пристрій ідеальним для розширених додатків для аудіо, відео та радіолокаційних сигналів.

2. Швидкісне спілкування та мережа

Швидкошвидкісні інтерфейси вводу/виводу FPGA та динамічна фазова вирівнювання (DPA) підтримують надійну передачу даних на рівні гігабіт.Він може впроваджувати протоколи зв'язку та функції фізичного шару для таких систем, як маршрутизатори, комутатори та взаємозв'язки задньої площини.Завдяки великій логічній здатності та гнучких PLL, він може керувати складними термінами та протоколами між множинними високошвидкісними інтерфейсами.Ці можливості роблять його сильним для телекомунікаційної інфраструктури та мережевого обладнання з високою пропускною здатністю.

3. Контролери пам'яті та системи обробки даних

EP2S60F672C4 підтримує різні інтерфейси зовнішньої пам'яті, включаючи DDR, DDR2, RLDRAM II та QDR II, що робить його ідеальним для розробки контролерів пам'яті з високою пропускною здатністю.Він може обробляти буферизацію даних, генерування та арбітраж з високою швидкістю з мінімальною затримкою.Поєднання швидких годинникових мереж та вбудованих блоків оперативної пам’яті дозволяє ефективно керувати великими потоками даних.Це робить FPGA придатним для обробки зображень, потокового потоку та наукових обчислювальних платформ, які покладаються на важку пропускну здатність даних.

4. Спеціальна логіка та вбудоване прискорення

Маючи понад 60 000 логічних елементів та багатих годинників, FPGA може розміщувати індивідуальні апаратні прискорювачі для конкретних алгоритмів.Дизайнери часто використовують його для розвантаження обчислювально інтенсивних завдань від процесорів, таких як шифрування, розбір протоколів або петлі управління в режимі реального часу.Він також може інтегрувати кілька функціональних блоків, що робить його придатним для складних конструкцій, подібних до SOC.Ця гнучкість робить його цінним у таких програмах, як промислова автоматизація, системи безпеки та аерокосмічні одиниці.

5. Платформи прототипування та освітнього розвитку

Пристрій EP2S60 зазвичай зустрічається на наборах розробки FPGA, що використовуються для прототипування, тестування та академічних досліджень.Його баланс логічної ємності, підрахунку вводу/виводу та можливості DSP дозволяють інженерам та студентам впроваджувати та перевіряти повні системи на одному мікросхемі.Він підтримує швидку ітерацію цифрових конструкцій, що дозволяє перевірити обладнання, перш ніж здійснювати розвиток ASIC.Багато університетів та науково -дослідних і науково -дослідних лабораторій використовують їх для викладання вдосконалених понять цифрового дизайну та обробки сигналів.

EP2S60F672C4 Подібні частини

|

Специфікація |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Сім'я / серія |

Стратікс II |

Стратікс II |

Стратікс II |

Стратікс II |

Стратікс II |

Стратікс II |

|

Логічні елементи (LE) |

60 440 |

60 440 |

60 440 |

60 440 |

60 440 |

60 440 |

|

Милостиня |

24 176 |

24 176 |

24 176 |

24 176 |

24 176 |

24 176 |

|

Пакет |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Швидкість |

C4 (std) |

C3 (швидше) |

C5 (швидше) |

C5 (швидше) |

I4 (std) |

I3 (швидше) |

|

Температура |

Комерційний (0 ~ 70 ° C) |

Комерційний |

Комерційний |

Комерційний |

Промисловий (−40 ~ 100 ° C) |

Промисловий (−40 ~ 100 ° C) |

|

Шпильки вводу/виводу |

492 |

492 |

492 |

492 |

492 |

492 |

|

Пам'ять на мікросхемі |

2,4 Мбіт |

2,4 Мбіт |

2,4 Мбіт |

2,4 Мбіт |

2,4 Мбіт |

2,4 Мбіт |

|

Основна напруга |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

|

Ключова різниця |

Базова комерційна швидкість |

C3 SPEED BIN, без свинцю "N" |

Вища швидкість контейнер |

Варіант з більш високою швидкістю, "N" |

Промислова температура, однакова щільність |

Промислова, швидша швидкість, без свинцю |

Етапи програмування EP2S60F672C4

Перш ніж використовувати FPGA EP2S60F672C4 FPGA, вам потрібно правильно налаштувати його зі своїм складеним Bitstream.Цей процес передбачає підготовку файлу програмування, налаштування апаратного інтерфейсу та забезпечення того, що конфігурація правильно завантажується на живлення.

Крок 1: Створіть та складайте свій дизайн

Ви починаєте з розробки логічного дизайну за допомогою програмного забезпечення Intel Quartus II.Після завершення дизайну ви збираєте його для створення файлу програмування (.sof або .pof) спеціально для пристрою EP2S60F672C4.Процес компіляції перевіряє терміни, призначення PIN -коду та використання ресурсів, щоб переконатися, що ваш дизайн вписується в архітектуру FPGA.Після складання вашого Bitstream готовий до конфігурації пристрою.

Крок 2: Налаштуйте обладнання програмування

Далі ви готуєте інтерфейс фізичного програмування між ПК та планою FPGA.Зазвичай це передбачає підключення USB-бластера або сумісного кабелю JTAG до порту JTAG пристрою.Ви повинні перевірити, що квартал II розпізнає програміст і чи правильно виявлено цільовий пристрій.Цей крок забезпечує стабільне спілкування перед ініціатором процесу конфігурації.

Крок 3: Завантажте файл програмування в пристрій

Використовуючи інструмент програміста Quartus II, ви додаєте складений файл .sof або .pof і виберете EP2S60F672C4 зі списку виявлених пристроїв.Потім ви ініціюєте послідовність програмування, під час якої Bitstream передається та завантажується в комірок конфігурації SRAM FPGA.Ви повинні стежити за панеллю прогресу та повідомленнями про стан, щоб підтвердити успішну конфігурацію.Після завершення FPGA починає негайно виконувати запрограмовану логіку.

Крок 4: Перевірте конфігурацію та операцію

Після програмування ви перевіряєте, що пристрій функціонує за призначенням.Quartus II надає опцію перевірки для перевірки CRC конфігурації та сигналів стану, гарантуючи, що конструкція завантажена правильно.Ви також можете перевірити свої функції вводу/виводу або запустити функціональне моделювання для підтвердження поведінки системи.Цей заключний крок гарантує, що ваш дизайн повністю працює та стабільно на апаратному забезпеченні.

EP2S60F672C4 Переваги та недоліки

Переваги

• Висока логічна щільність для складних конструкцій

• Хороше співвідношення продуктивності до витрат

• Легка міграція в одній родині

• Стабільні та зрілі інструменти розвитку

• Доведена надійність у промисловому використанні

Недоліки

• застарілий і важче для джерела

• Більш високе споживання електроенергії, ніж нові FPGAS

• Немає сучасних швидкісних приймачів

• Більш складне закриття часу при високому використанні

• Обмежена масштабованість для майбутніх протоколів

Розміри упаковки EP2S60F672C4

|

Тип |

Параметр |

|

Тип пакету |

672-FBGA (Fineline BGA) |

|

Розмір тіла (l × w) |

27,00 мм × 27,00 мм |

|

Загальна висота упаковки (a) |

Макс 3,50 мм |

|

Висота протистояння (A1) |

Мін 0,30 мм |

|

Товщина підкладки (A2) |

Макс 3,00 мм |

|

Діаметр кулі (B) |

0,50 мм - 0,70 мм |

|

Куля (E) |

1,00 мм |

|

Кількість кульок |

672 |

|

Стиль монтажу |

Поверхневе кріплення |

|

Опис пакету |

FBGA, сітка 27 × 27 мм |

EP2S60F672C4 Виробник

EP2S60F672C4 FPGA виробляється Корпорація Altera, провідний піонер у програмованих логічних пристроях.У 2015 році Altera придбала Інтель, і продукт зараз підпадає під групу програмованих рішень Intel (PSG), яка продовжує підтримувати та постачати створені сім'ї FPGA Altera.Intel підтримує лінію Stratix II як частину свого застарілого портфеля продуктів, забезпечуючи документацію, підтримку інструментів та довгострокову доступність для промислових та комунікаційних додатків.

Висновок

EP2S60F672C4 поєднує високу логічну щільність, гнучку архітектуру пам'яті та надійні функції вводу/виводу для підтримки складних цифрових систем.Його дизайн на основі ALM, пам'ять Trimatrix ™, блоки DSP та функції управління годинниками дозволяють ефективно впровадити вимогливі програми.Хоча він пропонує перевірену надійність та зрілу підтримку розвитку, він стикається з обмеженнями, такими як застарілість та відсутність сучасних приймачів порівняно з новішими поколіннями FPGA.В цілому, його збалансована продуктивність та універсальність роблять його надійним вибором для обробки сигналів, зв'язку, обробки даних та прототипування програм.

PDF -таблиця

EP2S60F672C4 ДАТЕЛИ:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Чи може EP2S60F672C4 працювати з сучасними інтерфейсами пам'яті DDR?

Так, він підтримує інтерфейси DDR, DDR2, QDR II та RLDRAM II, які охоплюють багато загальних стандартів зовнішньої пам'яті.Це робить його придатним для додатків для обробки даних з високою пропускною здатністю.

2. Чи потрібна EP2S60F672C4 Спеціальна обробка чи зберігання?

Так, як і інші компоненти, упаковані BGA, його слід зберігати в упаковці, що контролюється вологою, і обробляти захист від ОУР.Дотримуючись належних практик зберігання, допомагає підтримувати носіння та надійність пристроїв під час складання.

3. Як можна зменшити споживання електроенергії в проектах EP2S60F672C4?

Ви можете оптимізувати використання логіки, не використовувані годинники, знижувати напруги вводу-виводу, де це можливо, та використовувати параметри синтезу, усвідомленого потужністю, у кварталі II, щоб мінімізувати загальний залучення потужності.

4. Які інструменти програмування потрібні для EP2S60F672C4?

Вам знадобиться програмне забезпечення Intel Quartus II для дизайну, компіляції та програмування, а також USB-BLASTER або сумісний кабель JTAG для налаштування пристрою.

5. Чи підтримує EP2S60F672C4 оновлення поля або віддалену реконфігурацію?

Так, він підтримує шифрування Bitstream на основі AES та віддалену реконфігурацію, що дозволяє надійно оновлювати свою систему без фізичного заміни FPGA.

Все про lfxp6c-3fn256c ґратний напівпровідник

на 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT, ОСОБЛИВОСТІ, Посібник з програмування та таблиць даних

на 2025/10/3

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/19 147780

-

USB-C Pinout та функції

на 2000/04/19 112050

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/19 111352

-

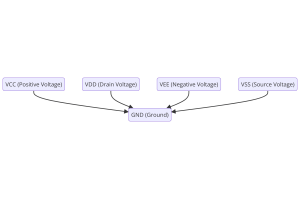

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/19 83806

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79608

-

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66991

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63113

-

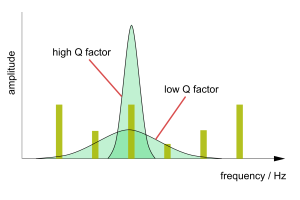

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63050

-

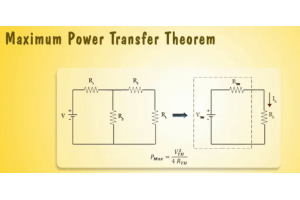

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54097

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52199