XC2C256-7TQ144C CPLD: PINOUT, ОСОБЛИВОСТІ, Посібник з програмування та таблиць даних

У цьому посібнику ви зрозумієте чіткий погляд на XC2C256-7TQ144C, низьку потужність CPLD від родини Coolrunner-II Xilinx (тепер AMD).Ви дізнаєтесь про його конфігурацію PIN-код, моделі CAD та основні функції, такі як логічна ємність, параметри вводу/виводу, підтримка напруги та функції економії електроенергії.Ми також пройдемо його архітектуру, криву вводу/V та технічні характеристики, а потім додатки, подібні частини, кроки програмування, переваги та недоліки, деталі упаковки та інформацію про виробника, щоб ви могли точно зрозуміти, як цей пристрій вписується у ваші проекти.Каталог

Що таке XC2C256-7TQ144C?

З XC2C256-7TQ144C -це низька потужність CPLD (складний програмований логічний пристрій) із родини Coolrunner-II Xilinx, яка зараз є частиною AMD.Він має 256 макроцеллів і поставляється в 144-контактному пакеті TQFP, призначеного для швидкої, детермінованої роботи з мінімальним споживанням електроенергії.Працюючи на ядрі 1,8 В, він пропонує надійну продуктивність у компактному формуваному факторі і добре підходить для конструкцій, що потребують миттєвої можливості та ефективної реалізації логіки.Як частина універсальної серії Coolrunner-II, вона виграє від перевіреної архітектури та широкої сумісності дизайну.

Шукаєте XC2C256-7TQ144C?Зверніться до нас, щоб перевірити поточні акції, час виконання та ціни.

Xc2c256-7tq144c pin-ux-схема

Діаграма PIN-OUT XC2C256-7TQ144C показує, як 144 шпильки розташовані для функцій Power, Ground, JTAG та запрограмованих користувачем.Більшість штифтів - це введення/вивод, які можна налаштувати як входи або виходи, і рівномірно розподіляються для підтримки гнучкої маршрутизації.Штифти VCC, VCCIO1, VCCIO2, VAUX та GND розміщуються навколо упаковки для забезпечення стабільного розподілу електроенергії та декількох варіантів напруги вводу/виводу.Штифти JTAG (TDI, TDO, TMS, TCK) згруповані для легкого програмування та тестування в системі.

Моделі CAD XC2C256-7TQ144C

Символ XC2C256-7TQ144C

XC2C256-7TQ144C Слід

XC2C256-7TQ144C 3D-модель

Особливості XC2C256-7TQ144C

• Тип пристрою та сім'я

XC2C256-7TQ144C-це складний програмований логічний пристрій (CPLD), який належить до сімейства Coolrunner-II, розробленому Xilinx (тепер AMD).Він призначений для низького споживання електроенергії, зберігаючи швидку, детерміновану логічну продуктивність, що робить його ідеальним для контрольної логіки та інтерфейсних програм.

• Логічна здатність

Цей пристрій містить 256 макроцелів, які є програмованими логічними ресурсами в CPLD.Ці макроцелі можуть бути налаштовані для реалізації різних комбінаційних та послідовних логічних функцій, надаючи помірну ємність для контролю, логіки клею та інтерфейси шини.

• Логічні блоки (функціональні блоки)

Він інтегрує 16 функціональних блоків, які організовують та керують групами макроцелів.Кожен блок пропонує локальні ресурси взаємозв'язку та продукції, що дозволяє гнучко реалізувати логіку та ефективну маршрутизацію в пристрої.

• Шпильки користувача вводу/виводу

XC2C256-7TQ144C пропонує до 118 шпильок вводу/виводу у своєму пакеті TQFP-144.Цей високий кількість штифтів дозволяє пристрою одночасно взаємодіяти з декількома підсистемами, що робить його придатним для складних конструкцій рівня плати.

• Основна напруга (VCC)

Основа працює в номінальному діапазоні 1,8 В (від 1,7 В до 1,9 В), що допомагає зменшити споживання електроенергії порівняно зі старими 5 В CPLDS.Ця нижня напруга корисна в сучасних цифрових системах змішаної напруги.

• Підтримка багато напруги вводу/виводу

Банки вводу/виводу підтримують декілька стандартів напруги, включаючи 1,5 В, 1,8 В, 2,5 В та 3,3 В. Ця гнучкість дозволяє CPLD безпосередньо взаємодіяти з компонентами, що працюють на різних рівнях напруги без перемикачів зовнішнього рівня.

• Високошвидкісна робота

З типовою затримкою розповсюдження штифтів до 5,7 нс (швидкісна ступінь “-7”), пристрій забезпечує швидку, детерміновану продуктивність.Це робить його придатним для критичних термінів, таких як декодування адрес, арбітраж шини та контроль.

• Низьке споживання електроенергії

Серія Coolrunner-II відома надзвичайно низькими струмами в режимі очікування, часто в діапазоні мікромамби.Ця низька статична потужність у поєднанні з динамічними функціями економії електроенергії дозволяє ефективно використовувати XC2C256-7TQ144C в системах, що працюють на батареї.

• Технологія Datagate

Ця функція дозволяє відключити не використовувані входи, запобігаючи непотрібному перемиканню та зменшенню динамічного споживання електроенергії.Він цінний у програмах, де певні сигнали неактивні протягом тривалих періодів.

• Програмування JTAG в системі

Пристрій підтримує IEEE 1149.1 (JTAG) та IEEE 1532 для програмування в системі.Це означає, що CPLD може бути налаштований, протестований та перепрограмований, не видаляючи його з дошки, спрощуючи розробку та оновлення.

• Вдосконалена структура клопотання

XC2C256-7TQ144C включає кілька глобальних годин, годинникових роздільників та спрацьованих подвійних регістрів.Він також забезпечує глобальний набір/скидання та локальне залучення на макроцелл, надаючи гнучкий контроль над термінами та синхронізацією.

• Входи Schmitt-тригер

Вибрані вхідні штифти можна налаштувати як Schmitt запускає для поліпшення шумового імунітету.Це корисно для обробки повільних або галасливих вхідних сигналів без додавання зовнішньої кондиціонерної схеми.

• Гнучкі результати виходу

Виходи підтримують тридержавну операцію, контроль швидкості, що знаходяться у ряді, конфігурації відкритих відбігів та додаткових підтяжок.Ці варіанти полегшують адаптацію CPLD до різних стандартів шини та умов зовнішнього навантаження.

• Розширена матриця взаємозв'язку (AIM)

Розширена матриця взаємозв'язку ефективно пов'язує функціональні блоки, що забезпечує повну маршрутизацію продукту через пристрій.Це покращує гнучкість логіки та допомагає підтримувати передбачувані показники часу.

CoolRunner-II CPLD Архітектура

Архітектура CoolRunner-II CPLD XC2C256-7TQ144C побудована навколо функціональних блоків, блоків вводу/виводу та розширеної матриці взаємозв'язку (AIM).Кожен функціональний блок містить макроцелі та програмований логічний масив (PLA), які впроваджують визначену користувачем логіку, тоді як мета ефективно переводить сигнали між блоками.Вводу/виводу блокує внутрішню логіку із зовнішніми штифтами, а також спеціалізованими схеми JTAG та BSC/ISP підтримують програмування та тестування.Ця структурована та взаємопов'язана архітектура дозволяє швидко, детерміновану продуктивність з низьким споживанням електроенергії, що робить її ідеальною для контролю, взаємодії та логіки клею в цифрових системах.

Типова крива I/V для XC2C256

Типова крива I/V для XC2C256-7TQ144C ілюструє залежність між вихідною напругою (VO) та вихідним струмом (IO) для різних напруг живлення вводу/виводу (1,5 В, 1,8 В, 2,5 В та 3,3 В).Зі збільшенням напруги живлення пристрій може джерело або протопити більш високі струми до того, як вихідна напруга почне значно падати.Така поведінка важлива для розуміння можливості приводу CPLD при взаємодії із зовнішніми компонентами, забезпечуючи, щоб рівні сигналу залишалися дійсними під навантаженням.Багато хто використовує цю криву для вибору відповідних напруг вводу/виводу та забезпечення надійної роботи в додатках, які вимагають конкретних сильних сил, що керує струмом.

Специфікація XC2C256-7TQ144C

|

Тип |

Параметр |

|

Виробник |

AMD/XILINX |

|

Серія |

Coolrunner II |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Програмований тип |

В системному програмованому |

|

Затримка часу TPD (1) Макс |

6,7 нс |

|

Постачання напруги - внутрішнє |

1,7 V ~ 1,9 V |

|

Кількість логічних елементів/блоків |

16 |

|

Кількість макроцелів |

256 |

|

Кількість воріт |

6000 |

|

Кількість вводу/виводу |

118 |

|

Робоча температура |

0 ° C ~ 70 ° C (TA) |

|

Монтажний тип |

Поверхневе кріплення |

|

Пакет / кейс |

144-LQFP

|

|

Пакет пристроїв постачальника |

144-TQFP (20 × 20) |

|

Базовий номер товару |

XC2C256 |

Програми XC2C256-7TQ144C

1. Логіка клею та мостовий інтерфейс

XC2C256-7TQ144C ідеально підходить для реалізації логіки клею, яка з'єднує та координує сигнали між різними цифровими компонентами.Він може обробляти такі функції, як декодування адрес, арбітраж шини та переклад протоколу, що дозволяє плавно зв’язати між мікроконтроллерами, пам'яттю, датчиками та іншими периферійними пристроями.Його передбачувані терміни та швидкі затримки шпильки забезпечують надійне взаємозв'язок навіть у складних конструкціях дошки.

2. Пристрої з низькою потужністю та акумулятором

Завдяки технології швидкої нульової потужності (FZP) та дуже низькому режимі очікування, цей CPLD дуже підходить для портативної та акумуляторної електроніки.Він може постійно залишатися живленням, вживаючи мінімальну енергію, що робить її ідеальною для завжди контрольних або моніторингових ланцюгів.Ви можете ще більше зменшити використання потужності за допомогою таких функцій, як Datagate, що мінімізує динамічне комутацію, коли входи неактивні.

3. Логіка управління та секвенування

Пристрій переважає при впровадженні машин кінцевого стану, контролю часу та послідовності сигналу, необхідних у багатьох вбудованих системах.Його детермінована, неутолітна архітектура дозволяє логіці управління стати активною відразу після живлення без затримки конфігурації.Це робить його сильним вибором для логіки скидання, схем руконизу та інших критичних часових завдань.

4. Вбудована підтримка системи та периферійна логіка

У вбудованих конструкціях XC2C256-7TQ144C може виступати як настроюється мікросхема підтримки, впроваджуючи спеціалізовані інтерфейси або розширюючи можливості мікроконтролера.Він може обробляти протоколи зв'язку, такі як SPI, I²C або UART, генерувати вибирання мікросхем або керувати маршрутизацією переривання.Вивантажуючи ці функції з процесора, він спрощує розробку програмного забезпечення та покращує загальну продуктивність системи.

Xc2c256-7tq144c подібні частини

|

Специфікація |

XC2C256-7TQ144C |

XC2C256-7TQ144i |

XC2C256-7TQG144i |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Сім'я пристроїв |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

CoolRunner-II CPLD |

|

Логічна щільність (макроцелі) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Тип пакету |

TQFP-144 |

TQFP-144 |

TQFP-144 (без Pb) |

VQFP-100 |

VQFP-100 (без Pb) |

TQFP-144 |

|

Швидкість |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (швидше) |

|

Діапазон температури |

Комерційний (0 - 70 ° C) |

Промисловий (-40-85 ° C) |

Промисловий (-40-85 ° C) |

Комерційний (0 - 70 ° C) |

Комерційний (0 - 70 ° C) |

Комерційний (0 - 70 ° C) |

|

Вводу/вир. |

118 |

118 |

118 |

80 |

80 |

118 |

|

Основна напруга (VCC) |

1,8 V |

1,8 V |

1,8 V |

1,8 V |

1,8 V |

1,8 V |

|

Підтримка напруги вводу/виводу |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

|

Дотримання / без Pb |

Стандартний |

Стандартний |

PB-Free / RoHS |

Стандартний |

PB-Free / RoHS |

Стандартний |

|

Відмінності |

Базова комерційна версія |

Промислова температура версії |

Промислова + PB-без PB версія |

Менший пакет, менше вводу/виводу |

Менша версія без PB |

Швидша версія часу |

Етапі програмування XC2C256-7TQ144C

Програмування XC2C256-7TQ144C-це прямий процес, який передбачає підготовку вашої конструкції, генерування файлу програмування та завантаження його в CPLD через JTAG.Дотримуючись кожного кроку уважно, ви можете забезпечити успішну конфігурацію та належну роботу пристроїв на своїй платі.

1. Дизайн та синтез

Ви починаєте з написання логічного дизайну за допомогою HDL (VHDL або Verilog) або схематичного запису.Після завершення дизайну ви запускаєте процес синтезу, який перетворює вашу логіку у внутрішню структуру макроцелі та взаємозв'язків пристрою.Цей крок гарантує, що ваш дизайн сумісний з архітектурою XC2C256 та готовим до впровадження.

2. Місце та маршрут / реалізація (підгонка)

Далі ви виконуєте місце та маршрут, також відомі як Fitting, який призначає вашу синтезовану логіку фактичним фізичним макроелеям та ресурсам маршрутизації всередині CPLD.Інструмент перевіряє обмеження термінів, вирішує використання ресурсів та оптимізує шляхи, щоб відповідати продуктивності вашого дизайну.Це гарантує, що схема буде надійно запущена після запрограмування в пристрій.

3. Створіть файл програмування

Після завершення реалізації ви генеруєте файл програмування (біт, варення або формат SVF), який містить точні дані конфігурації для пристрою.Цей файл представляє, як кожен макроцелл, взаємозв'язок та вводу/виводу налаштовано для реалізації вашої логіки.Перед тим, як переходити до фактичного програмування пристроїв, потрібно готовий цей файл.

4. Програмування JTAG / In-System

Нарешті, ви підключаєте пристрій до ПК за допомогою кабелю програмування JTAG та відкриваєте інструмент впливу Xilinx (або еквівалент).Потім ви завантажуєте генерований файл програмування та завантажуєте його в XC2C256-7TQ144C через шпильки JTAG (TDI, TDO, TCK, TMS).Після завершення процесу CPLD негайно починає працювати з вашою запрограмованою логікою, не вимагаючи циклу живлення або пам'яті зовнішньої конфігурації.

Xc2c256-7tq144c переваги та недоліки

Переваги

• Дуже низька потужність в режимі очікування, ідеально підходить для конструкцій, що працюють на батареї.

• Миттєва операція без затримки конфігурації.

• Передбачуваний термін для легшого закриття дизайну.

• Замінює кілька дискретних логічних мікросхем, економлять простір та вартість.

• Підтримує кілька напруг вводу/виводу без перемикачів зовнішнього рівня.

Недоліки

• Обмежена логічна ємність порівняно з більшими CPLD або FPGA.

• Немає вбудованих DSP, оперативної пам’яті або високошвидкісних приймачів.

• Ставши застарілим, ускладнюючи майбутнє пошуку.

• Нижня стеля продуктивності для високошвидкісних застосувань.

• Менша гнучкість маршрутизації для складних або нерегулярних конструкцій.

Розміри упаковки XC2C256-7TQ144C

|

Тип |

Параметр |

|

Тип пакету |

TQFP-144 |

|

Розмір тіла упаковки |

20 мм × 20 мм |

|

Свинцева крок |

0,5 мм |

|

Кількість шпильок |

144 |

|

Висота упаковки (макс) |

1,4 мм |

|

Товщина упаковки (номінальна) |

1,0 мм |

|

Довжина свинцю |

0,45 мм ~ 0,75 мм |

|

Ширина свинцю |

0,17 мм ~ 0,27 мм |

|

Монтажний тип |

Поверхневе кріплення |

|

Пакет пристроїв постачальника |

144-TQFP (20 × 20) |

XC2C256-7TQ144C Виробник

XC2C256-7TQ144C виробляється Xilinx, провідна компанія в програмованих логічних рішеннях.Xilinx широко визнаний для піонерських технологій FPGA та CPLD, що забезпечує надійні та високоефективні пристрої для промислових, комерційних та споживчих програм.Сьогодні Xilinx працює в рамках AMD, продовжуючи доставляти передові програмовані логічні продукти з сильною довгостроковою підтримкою та інноваціями.

Висновок

XC2C256-7TQ144C виділяється за низьким споживанням електроенергії, швидкою детермінованою продуктивністю та гнучкістю вводу/виводки багато напруги, що робить його надійним вибором для сучасних цифрових конструкцій.Його збалансована комбінація 256 макроцелів, 118 вводу/виводу штифтів та вдосконаленої архітектури взаємозв'язку підтримує широкий спектр функцій управління, взаємодії та клею.Завдяки підтримці програмування в системах, функціях економії живлення Datagate та надійних конфігурацій вводу/виводу, він плавно інтегрується в вбудовані системи та середовища змішаної напруги.

PDF -таблиця

XC2C256-7TQ144C ДАТЕЛИ:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1. Чи потрібна xc2c256-7tq144c пам'яті зовнішньої конфігурації?

Ні. Однією з його переваг є миттєва операція.Конфігурація зберігається внутрішньо, тому вона спрямовується готовою до запуску без будь -якої зовнішньої випускної або флеш -пам'яті.

2. Які інструменти програмування сумісні з XC2C256-7TQ144C?

Ви можете запрограмувати пристрій за допомогою програмного забезпечення Xilinx Impact за допомогою кабелю програмування JTAG.Багато хто також використовує сумісних сторонніх програмістів JTAG, але переконайтеся, що вони підтримують стандарти IEEE 1149.1/1532.

3. Чи може XC2C256-7TQ144C замінити кілька дискретних логічних ІМ у вашому дизайні?

Так.Завдяки 256 макроцеллам та гнучким вводу/виводу, цей CPLD може інтегрувати кілька функцій логіки та управління клеєм в один пристрій, що допомагає зменшити простір та кількість компонентів.

4. Чи підходить XC2C256-7TQ144C для додатків для акумуляторів з низькою потужністю?

Так.Завдяки технології швидкої нульової потужності (FZP) та дуже низькому режимі очікування, вона ідеально підходить для завжди на ланцюгах, портативних пристроях та вбудовуваних системах.

5. Чи можете ви використовувати XC2C256-7TQ144C для високошвидкісної обробки сигналів?

Він не призначений для швидкісних завдань DSP або приймачів.Незважаючи на те, що він забезпечує швидкі затримки штифтів до шпильки, він найкраще підходить для контролю, взаємодії та логіки часу, а не складної обробки даних.

EP2S60F672C4 FPGA: Особливості, програми, Посібник з програмування та даних

на 2025/10/4

EPM3256AFC256-7 Огляд CPLD: Особливості, Покін, Програмування та програми

на 2025/10/3

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/19 147781

-

USB-C Pinout та функції

на 2000/04/19 112051

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/19 111352

-

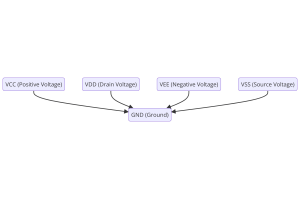

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/19 83806

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79610

-

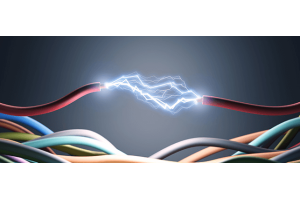

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66991

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63113

-

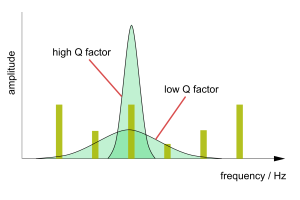

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63051

-

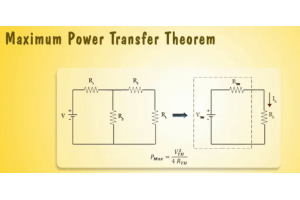

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54097

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52200