EPM7256AETC144-10N CPLD: Посібник з даних, технічних характеристик, додатків та програмування

EPM7256AETC144-10N-це програмований логічний пристрій (CPLD) із серії Max® 7000A Intel.Цей чіп призначений для швидкої продуктивності, працює на до 172,4 МГц із затримкою 10 нс.Цей посібник пояснює все про цей CPLD, включаючи його функції, специфікації, використання, як його програмувати та його макет PIN -коду.Якщо вам потрібен надійний, програмований чіп для цифрових схем, ця стаття допоможе вам зрозуміти, як вона працює.Каталог

EPM7256AETC144-10N Опис

З EPM7256AETC144-10n є високоефективним CPLD від серії Max® 7000A Intel, пристосованою для вимогливих завдань з інтеграції логіки.Цей пристрій може похвалитися 256 макроцеллами та близько 5000 корисних воріт, що сприяє значній гнучкості та корисності дизайну у складних цифрових умовах.Працюючи з максимальною частотою 172,4 МГц із затримкою поширення лише 5,5 нс, вона розроблена для швидкої роботи.Розроблений з 3,3 В робочою напругою та упакованою у компактній 144-контактній тонкій квадроциклій площі (TQFP), EPM7256AETC144-10N підтримує надійні вимоги до проектування логіки.EPM7256AETC144-10N використовує пам'ять неноментної конфігурації на основі EEPROM, що забезпечує постійне зберігання даних про програмування.Ця функція в поєднанні з програмованою в системі через інтерфейс JTAG забезпечує легкість у оновленні та перепрограмуванні поля, посилюючи довгострокову зручність використання без необхідності фізичної реконфігурації чи заміни.

Забезпечте свої проекти надійною технологією, що підтверджує поле, влаштувавши з нами об'ємне замовлення для EPM7256AETC144-10N та забезпечення суцільного рішення CPLD.

EPM7256AETC144-10N CAD Моделі

EPM7256AETC144-10N символ

EPM7256AETC144-10N Слід

EPM7256AETC144-10N 3D-модель

EPM7256AETC144-10N Особливості

Макроцелі:Цей пристрій оснащений 256 макроцеллами.Макроцелі - це налаштовані логічні компоненти, які дозволяють CPLD виконувати різні логічні функції.

Корисні ворота:Він забезпечує приблизно 5000 корисних воріт.Це стосується еквівалентної кількості основних логічних воріт (наприклад, і, або, ні), які можна налаштувати в пристрої.

Шпильки вводу/виводу:CPLD має 120 вхідних/вихідних штифтів, що дозволяє проводити широке взаємозв'язок з іншими частинами електронної конструкції користувача.

Затримка про поширення (TPD):Максимальна затримка розповсюдження - 10 наносекунд, що визначає, наскільки швидко CPLD може обробляти вхідні сигнали та виробляти виходи.

Робоча частота:Він може працювати на частотах до 95,2 МГц, що визначає швидкість, з якою пристрій може виконувати логічні операції.

Напруга живлення:Пристрій працює при напрузі живлення 3,3 В, що вирівнюється із загальними рівнями цифрової логіки низької напруги.

Пакет:Він поставляється в 144-контактному тонкому квадроциклу (TQFP), компактному типу пакету, який сприятливий для мінімізації місця, необхідного на друкованих платах.

Діапазон робочої температури:Діапазон робочої температури становить від 0 ° С до 70 ° C, забезпечуючи надійну продуктивність у широкому діапазоні умов навколишнього середовища.

Програмність в системі:CPLD підтримує програму в системі через IEEE STD.1149.1 Інтерфейс спільної тестової групи (JTAG), що дозволяє програмувати та перепрограмувати логічний пристрій в кінцевій конфігурації обладнання.

EPM7256AETC144-10N Блок-схема

З EPM7256AETC144-10n є Складний програмований логічний пристрій (CPLD) з чотирма Логічні блоки масиву (лабораторії) , кожен з яких містить 16 макроцелів, що загалом 64 макроцелі.Ці макроцелі обробляють як комбінаційну, так і послідовну логіку, що робить пристрій гнучким для різних цифрових логічних програм.В центрі CPLD знаходиться Програмований масив взаємозв'язків (PIA), який з'єднує всі лабораторії, забезпечуючи ефективну маршрутизацію сигналу.Кожна лабораторія спілкується з PIA за допомогою 36 ліній взаємозв'язку, що дозволяє ефективно ділитися та обробляти сигнали.Пристрій має блоки управління вводу/виводу з кожної сторони, підтримуючи шпильки від 2 до 16 вводу/виводу на лабораторію.Ці блоки допомагають керувати вхідними та вихідними функціями, підключаючи CPLD до зовнішніх схем.Контрольні сигнали, такі як глобальні годинники (GCLK1, GCLK2), Вихід Увімкнення (OE1) та глобальне скидання (GCLRN) допомагають синхронізувати логічні операції на пристрої.Крім того, логічні ворота керують годинниками та скиданням сигналів, забезпечуючи плавну роботу.Цей CPLD розроблений для швидкісної логічної обробки, пропонуючи програмованість, ефективну маршрутизацію сигналу та надійний контроль вводу/виводу, що робить його придатним для вбудованих систем, комунікацій та промислової автоматизації.

Технічні характеристики EPM7256AETC144-10N

|

Тип |

Параметр |

|

Виробник |

Altera/Intel |

|

Серія |

MAX® 7000a |

|

Упаковка |

Лоток |

|

Статус частини |

Застарілий |

|

Програмований тип |

В системному програмованому |

|

Затримка часу TPD (1) Макс |

10 нс |

|

Постачання напруги - внутрішнє |

3V ~ 3,6 В |

|

Кількість логічних елементів/блоків |

16 |

|

Кількість макроцелів |

256 |

|

Кількість воріт |

5000 |

|

Кількість вводу/виводу |

120 |

|

Робоча температура |

0 ° C ~ 70 ° C (TA) |

|

Монтажний тип |

Поверхневе кріплення |

|

Пакет / кейс |

144-LQFP |

|

Пакет пристроїв постачальника |

144-TQFP (20x20) |

|

Базовий номер товару |

EPM7256 |

EPM7256AETC144-10N програми

Штучний інтелект

Цей CPLD використовується в апаратних прискорювачі AI для ефективного обробки складних обчислень, необхідних для обробки алгоритмів AI, підвищуючи як швидкість, так і надійність програм AI.

5G технологія

У царині 5G комунікацій EPM7256AETC144-10N найкраще підходить для обробки сигналів та управління протоколами зв'язку.Його високошвидкісні логічні операції полегшують швидку обробку, необхідну в наступному поколінні бездротових систем.

Хмарні обчислення

У центрах обробки даних цей пристрій покращує можливості обробки, слугуючи компонентом для управління великими обсягами даних та складними обчисленнями, підтримуючи інфраструктуру хмарних служб.

Побутова електроніка

CPLD знаходить додатки в побутовій електроніці, таких як телевізори та ігрові консолі, де він виконує спеціальні логічні функції, що покращують функціональні можливості та досвід пристрою.

Бездротова технологія

Він використовується в пристроях бездротового зв'язку для модуляції та демодуляції сигналів, забезпечуючи ефективне та ефективне спілкування в таких пристроях, як маршрутизатори та стільникові модеми.

Промисловий контроль

Цей пристрій є невід'ємним для систем автоматизації в промислових умовах, де він керує машинами та керує процесами, сприяючи підвищенню продуктивності та безпеки.

Інтернет речей (IoT)

У пристроях IoT EPM7256AETC144-10N керує завданнями обробки та зв'язку даних, що чудово підходить для безшовної роботи підключених пристроїв у розумних будинках та галузях.

Медичне обладнання

CPLD застосовується в медичних пристроях для таких завдань, як збору даних та обробка сигналів, відіграючи роль у надійності та ефективності медичної діагностики та обладнання для лікування.

EPM7256AETC144-10n Подібні частини

EPM7256AETC144-10N Переваги

Висока логічна щільність

Цей пристрій упаковує 256 макроцелів і приблизно 5000 корисних воріт, що дозволяє здійснити складні логічні схеми в межах однієї мікросхеми.Ця висока логічна щільність полегшує більш інтегровану та компактну конструкцію, зменшуючи загальну кількість компонентів та спрощуючи макети плати.

Програмність в системі (провайдер)

За участю програмованості в системі через IEEE STD.1149.1 Інтерфейс JTAG, EPM7256AETC144-10N дозволяє легко програмувати та перепрограмувати безпосередньо в ланцюзі.Ця здатність є неоціненною для швидкого прототипування та ітеративних процесів проектування, що дозволяє вносити корективи, не потребуючи заміни мікросхеми.

Швидка затримка розповсюдження

З максимальною затримкою розповсюдження всього 10 нс, цей CPLD забезпечує швидку обробку входів та результатів для додатків, які потребують високошвидкісної обробки даних та своєчасних відповідей, таких як обробка відео та високочастотні системи торгівлі.

Низьке споживання електроенергії

Працюючи на напрузі живлення 3,3 В, EPM7256AETC144-10N оптимізований для енергоефективності.Це низьке споживання електроенергії вигідно в портативних та акумуляторних пристроях, де управління електроенергією добре для продовження експлуатаційного терміну експлуатації.

Всебічні можливості вводу/виводу

Пристрій оснащений шпильками 120 вводу/виводу, що забезпечує широкі варіанти підключення.Це дозволяє гнучко взаємодіяти з широким спектром периферійних пристроїв та іншими системними компонентами, що робить його дуже адаптованим до складних багатодобових середовищ.

Ненуєльне сховище конфігурації

Завдяки своїй пам’яті на основі EEPROM, CPLD зберігає свої налаштування конфігурації навіть після вимкнення живлення, забезпечуючи, що функціональність пристрою залишається послідовною у циклах живлення.Ця функція необхідна для додатків, що потребують надійної, довгострокової продуктивності без необхідності частого перенастроювання.

Epm7256aetc144-10n етапи програмування

Програмування пристрою EPM7256AETC144-10N включає шестиступеневий процес програмування (ISP):

1. Введіть Інтернет -провайдер: Цей крок гарантує вхідні та вихідні частини пристрою перемикання від звичайного використання до режиму програмування плавно.Це займає близько 1 мілісекунд.

2. Перевірте ідентифікатор: Перед початком програмування пристрій перевіряє власний ідентифікатор.Цей крок дуже швидкий.

3. Основна стирання: це очищає всі попередні дані з пристрою.Це робиться, отримавши команду, щоб стерти все, а потім чекаючи 100 мілісекунд, щоб переконатися, що все стерти.

4. Програма: Тут вкладаються нові дані в пристрій.Для кожної частини даних він надсилається на правильну адресу в пристрої, а потім спеціальний імпульс гарантує, що він зберігається належним чином.

5. Перевірте: Після програмування пристрій перевіряє, чи всі дані правильно зберігаються, прочитавши його назад і порівнюючи його з тим, якими він повинен бути.

6. Вихід з питань провайдера: Цей крок перемикає пристрій назад з режиму програмування в режим звичайного використання.Це також займає близько 1 мілісекунд.

Загальний час, необхідний для програмування, залежить від того, як довго триває кожен імпульс і як швидкі дані можуть переміщатися в пристрій та поза ним, на що впливає швидкість годинного годинника та скільки даних для обробки.Різні пристрої можуть зайняти різну кількість часу, оскільки вони мають різну кількість пам'яті для програми.

EPM7256AETC144-10n Пакетна діаграма пакету

На діаграмі показано EPM7256AETC144-10N контур та нумерація штифтів.Цей чіп поставляється в TQFP-144 (тонкий квадроцикл з 144 шпильками), це означає, що він має вишукані потрясіння з усіх чотирьох сторін.Розташування штифта 1 позначається невеликою крапкою, а числа штифтів збільшують проти годинникової стрілки навколо упаковки.Ключові довідкові штифти, такі як PIN -код 1, PIN -код 37, PIN 73 та PIN 109, допомагають орієнтувати під час складання друкованої плати.Розміри контуру визначають фізичний розмір мікросхеми, щоб забезпечити належне встановлення друкованої плати.Розташування розвороту дозволяє ефективно маршрутизувати сигнал, що робить його придатним для складних логічних додатків.EPM7256AE є частиною серії MAX 7000A CPLD, що містить 256 макроцеллів та програмуваності в системній системі.Суфікс -10N вказує на 10 нс швидкості та пакет без свинцю.

EPM7256AETC144-10N Виробник

EPM7256AETC144-10N-це складний програмований логічний пристрій (CPLD), спочатку розроблений корпорацією Altera, який згодом був придбаний Корпорація Intel У 2015 році. З моменту придбання Intel став офіційним виробником продуктів FPGA та CPLD Altera, включаючи серію Max® 7000A, до якої належить цей пристрій.EPM7256AETC144-10N розроблений для високопродуктивних додатків, що підтримують програму в системі (ISP) через JTAG (IEEE 1149.1).Незважаючи на те, що Intel успадкувала технологію CPLD Altera, цей пристрій з тих пір був припинений і зараз класифікується як застарілий, тобто Intel більше не виробляє або підтримує його в активному виробництві.

Висновок

EPM7256AETC144-10N-це потужний і гнучкий CPLD, який використовується в AI, 5G, хмарних обчисленнях, промислових машинах, IoT та медичних пристроях.Він швидко обробляє дані, використовує невелику потужність і дозволяє легко перепрограмувати, не видаляючи їх з ланцюга.Це все ще корисно для старих конструкцій, які потребують програмованої логіки зі стабільною продуктивністю.Незалежно від того, чи працюєте ви з цим CPLD або шукаєте подібні альтернативи, розуміння його дизайну, програмування та переваг можуть допомогти вам найкраще використовувати його в високошвидкісних цифрових додатках.

PDF -таблиця

EPM7256AETC144-10N ДАТЕЛИ:

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Питання що часто задаються [FAQ]

1.

EPM7256AETC144-10N забезпечує 256 макроцелів і приблизно 5000 корисних воріт, що дозволяє здійснити помірно складні логічні реалізації.

2. Як я програмував EPM7256AETC144-10N, і які інструменти мені потрібні?

EPM7256AETC144-10N підтримує програму в системі (ISP) через інтерфейс JTAG (IEEE 1149.1).Вам знадобиться Altera USB-BLASTER або Intel Quartus Prime Software, щоб записати дані конфігурації на мікросхемі.

3. Які відмінності між EPM7256AETC144-10N та EPM7256AETC144-7?

Основна відмінність - швидкість.EPM7256AETC144-10N має максимальну затримку розповсюдження 10 нс, тоді як EPM7256AETC144-7 має швидшу затримку 7 нс для додатків з більш високою швидкістю.Обидва пристрої поділяють один і той же пакет, введення/виведення та структуру макроцелла.

4. Чи потрібен EPM7256AETC144-10N зовнішнього осцилятора?

Ні, сам CPLD не потребує зовнішнього осцилятора, але він підтримує зовнішні входи.Якщо ваша конструкція потребує точних термінів, для керування його логічними операціями може використовуватися зовнішній годинник.

5. Що робить EPM7256AETC144-10N відмінним від інших CPLD у серії Max 7000A?

Цей CPLD виділяється завдяки своїй швидкісній продуктивності (10 нс затримки розповсюдження), 256 макроцеллів та 5000 корисних воріт, що робить його ідеальним для складних логічних конструкцій.Він також підтримує програму в системі (ISP) через JTAG, на відміну від деяких старих моделей.

Процесор MPC8245LZU300D: таблиця даних, функції, додатки та технічні характеристики

на 2025/03/13

Простий посібник з батарейних батарей L1154 для повсякденного використання

на 2025/03/13

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147776

-

USB-C Pinout та функції

на 2000/04/18 112018

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111351

-

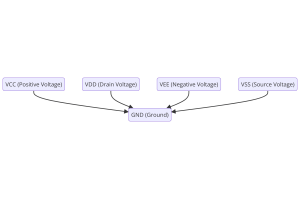

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83777

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79575

-

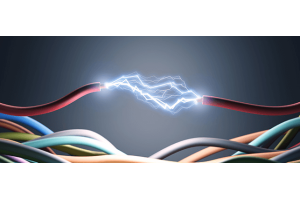

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66964

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63104

-

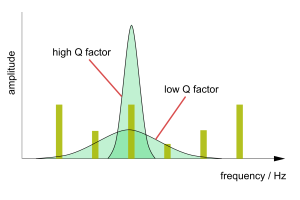

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63041

-

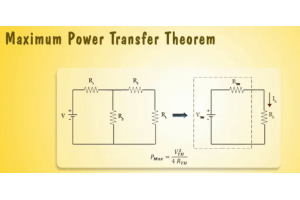

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54097

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52189