Поліпшення дизайну FPGA за допомогою файлів обмеження користувачів (UCF) для інструментів Xilinx ISE

Це посібник досліджує роль файлів обмежень користувачів (UCFS) у вдосконаленні дизайну FPGA за допомогою інструментів Xilinx ISE.UCFS дозволяє додати конкретні обмеження для кращого контрольного терміну, логіки та розміщення, що підвищує точність проектування, продуктивність та надійність.Показуючи, як ефективно застосувати ці обмеження, посібник допомагає спростити процес проектування, скоротити час налагодження та забезпечити успішну доставку проекту.Каталог

Мета та роль UCFS у дизайні FPGA

У дизайні FPGA файли обмеження користувачів (UCFS) відіграють роль у контролі того, як логіка, синтезована з вашого коду, фізично реалізується на мікросхемі.Ці файли дозволяють вказати важливі параметри, такі як обмеження термінів, призначення PIN -коду та деталі розміщення області, які можуть безпосередньо вплинути на те, відповідає дизайн вимогам чи ні.Подумайте про UCFS як про креслення, які гарантують, що все розміщується правильно, працює за графіком і акуратно вписується на місце.Процес встановлення обмежень починається на ранніх стадіях розвитку.Почніть із створення файлу UCF перед синтезом, гарантуючи, що параметри були зафіксовані з самого початку.Після синтезу генеруються додаткові файли обмеження, такі як файл обмеження NetList (NCF) та файл фізичних обмежень (PCF) для відображення змін, внесених до логіки, та доопрацювання фізичних обмежень.Кожен з цих файлів базується на попередньому кроці, поступово вдосконалюючи дизайн.UCFS-це текстові файли, записані у форматі ASCII, а це означає, що вони можуть бути відредаговані за допомогою основних текстових редакторів або більш спеціалізованих інструментів, таких як редактор обмеження Xilinx.Ця простота робить UCFS високодоступними та гнучкими, щоб зануритися в специфіку налаштувань обмеження, не потребуючи надмірно складних інструментів.

Як обмеження формують дизайн FPGA?

У дизайні FPGA обмеження відіграють роль у формуванні того, як чіп виконує та взаємодіє із зовнішніми пристроями.Ці обмеження визначаються у UCF (файл обмежень користувачів), який діє як детальний набір інструкцій для інструменту дизайну, вказуючи, як слід підключити та керувати внутрішніми компонентами FPGA.Основні обмеження включають обмеження термінів, які забезпечують сигнали проїзд між компонентами в певні часові рамки, щоб підтримувати надійну продуктивність з потрібною швидкістю тактової швидкості.Призначення PIN -коду Карти фізичних штифтів FPGA на зовнішні пристрої, такі як датчики, модулі пам'яті або інтерфейси зв'язку, забезпечуючи точні з'єднання.Обмеження області контролюють розміщення логічних блоків на мікросхемі, щоб уникнути заторів, зменшити затримки та оптимізувати використання ресурсів.Без цих обмежень автоматизовані інструменти прийматимуть рішення щодо розміщення та маршрутизації, але часто з неоптимальними результатами, що призводить до проблем з термінами, вузьких місць або неефективних макетів мікросхем.Використовуючи файли UCF, багато хто зберігає контроль над цими критичними аспектами, що призводить до кращої продуктивності, ефективності та надійності в конструкціях FPGA.

Ітеративна природа вдосконалення обмежень

Дизайн FPGA рідко-це одноразовий процес.Обмеження неодноразово регулюються протягом усього циклу розробки в міру розвитку дизайну і виникають нові виклики.Інші налаштовують файли UCF для досягнення цілей продуктивності, виправлення проблем з термінами або адаптації до зміни вимог проекту.Це ітеративне вдосконалення є важливою частиною робочого процесу FPGA.Наприклад, якщо ви помічаєте, що шлях сигналу займає занадто багато часу, щоб пропагувати між двома компонентами, вони можуть змінити UCF, щоб змінити обмеження терміну або перемістити ці компоненти для зменшення затримок.Аналогічно, якщо призначення PIN -коду суперечить зовнішнім обладнанням, UCF можна редагувати для вирішення невідповідності.Кожна редакція UCF наближає дизайн ближче до потрібного результату, причому кожна коригування навчає більше про компроміси, що беруть участь у оптимізації FPGA.Цей цикл тестування, коригування та навчання не тільки покращує дизайн, але й загострює навички.

Переваги використання UCFS

Застосування обмежень за допомогою файлів UCF забезпечує кілька практичних переваг, які сприяють успіху проектів FPGA:

• Поліпшена точність часу: добре складені обмеження термінів гарантують, що FPGA надійно працює з бажаною швидкістю тактової швидкості, уникаючи помилок, спричинених затримками сигналу.

• Краще використання ресурсів: Обмеження області запобігають розміщенню логічних блоків занадто близько один до одного або занадто далеко, оптимізуючи простір мікросхем та підвищення продуктивності.

• Спрощена налагодження: Контролюючи завдання PIN -коду та маршрутизацію сигналу, UCFS допомагає зменшити конфлікти маршрутизації, що полегшує діагностику та виправлення проблем під час тестування.

Про нас

ALLELCO LIMITED

Дізнайтеся більше

Швидкий запит

Будь ласка, надішліть запит, ми відповімо негайно.

Стандартні продукти, специфічні для додатків (ASSP): водіння інновацій у сучасній електроніці

на 2025/01/8

Система на програмованому чіпі (SOPC): технологія, дизайн та додатки

на 2025/01/8

Популярні публікації

-

Складні комп'ютери набору інструкцій: як вони змінили обчислення?

на 8000/04/18 147758

-

USB-C Pinout та функції

на 2000/04/18 111960

-

Використання xilinx Unified Dimulation Primitives: Вичерпне посібник з дизайну та моделювання FPGA

на 1600/04/18 111349

-

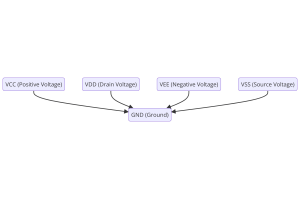

Напруга джерела живлення в електроніці: значення VCC, VDD, VEE, VSS і GND

на 0400/04/18 83726

-

Посібник з роз'єму RJ45: Покін, проводка, типи кабелів та використання

на 1970/01/1 79511

-

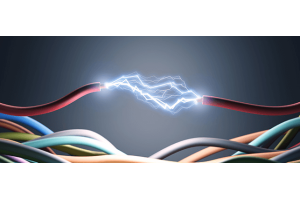

Кінцевий посібник з дротяних кольорових кодів у сучасних електричних системах

Те, як наші електричні системи використовують кольори, - це не лише зовнішній вигляд.Кожен колір дроту тепер вказує на певну функцію, що полегшує ідентифікацію та обробку електричних компонентів пр...на 1970/01/1 66929

-

Посібник з очищення клапана: функція, симптоми, тестування та заміна для оптимальних показників двигуна

Клапан Purege є ключовою частиною системи автомобіля, яка допомагає підтримувати повітря в чистоті, керуючи пари палива, перш ніж вони зможуть втекти в атмосферу.Це не тільки допомагає навколишньом...на 1970/01/1 63078

-

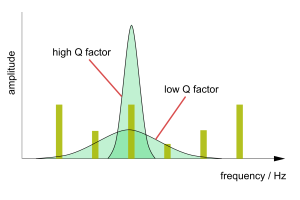

Якість (Q) Фактор: рівняння та додатки

Коефіцієнт якості, або "Q", важливий при перевірці того, наскільки добре індуктори та резонатори працюють в електронних системах, які використовують радіочастоти (RF)."Q" вимірює, наскільки добре л...на 1970/01/1 63019

-

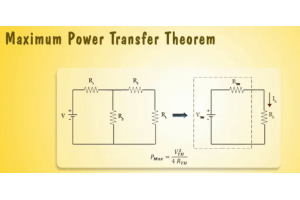

Досягнення пікових показників з максимальною теоремою передачі потужності

Максимальна теорема передачі потужності пояснює, як енергія від джерела, наприклад акумулятора або генератора, переходить до підключеного навантаження.Він показує точну умову, коли навантаження отр...на 1970/01/1 54086

-

Технічні характеристики акумулятора A23 та сумісність

Акумулятор A23-це невеликий акумулятор у формі циліндра з високою напругою.Також називається 23A, 23AE або MN21, він працює на 12 вольт і набагато вище, ніж батареї AA або AAA.Його спеціал...на 1970/01/1 52156